Warning message

Features

- Generates up to four independent output frequencies with a total of 7 differential outputs and one reference LVCMOS output

- Supports multiple differential output I/O standards:

- Three universal output pairs with each configurable as one differential output pair (LVDS, LVPECL, or regular HCSL) or two LVCMOS outputs. The frequency of each output pair can be individually programmed

- Four copies of Low Power HCSL (LP-HCSL) outputs

- Meets PCIe® Gen 1/2/3, USB 3.0, 1/10 GbE clock requirements

- <0.7ps RMS typical phase jitter on outputs

- Four fractional output dividers (FODs)

- Independent spread spectrum capability from each fractional output divider

- Stores 4 different configurations in OTP non-volatile memory

- Input frequency ranges up to 200MHz

- Output frequency ranges up to 350MHz

- Programmable loop bandwidth and crystal load capacitance

- 1.8V/2.5V/3.3V core and output voltages

- Supported by the Timing Commander™ software tool

Description

The 5P49V5907 is a programmable clock generator intended for high-performance consumer, networking, industrial, computing, and data communications applications. Configurations may be stored in on-chip One-Time Programmable (OTP) memory or changed using the I2C interface. This is Renesas' fifth generation of programmable clock technology (VersaClock® 5). The frequencies are generated from a single reference clock or crystal.

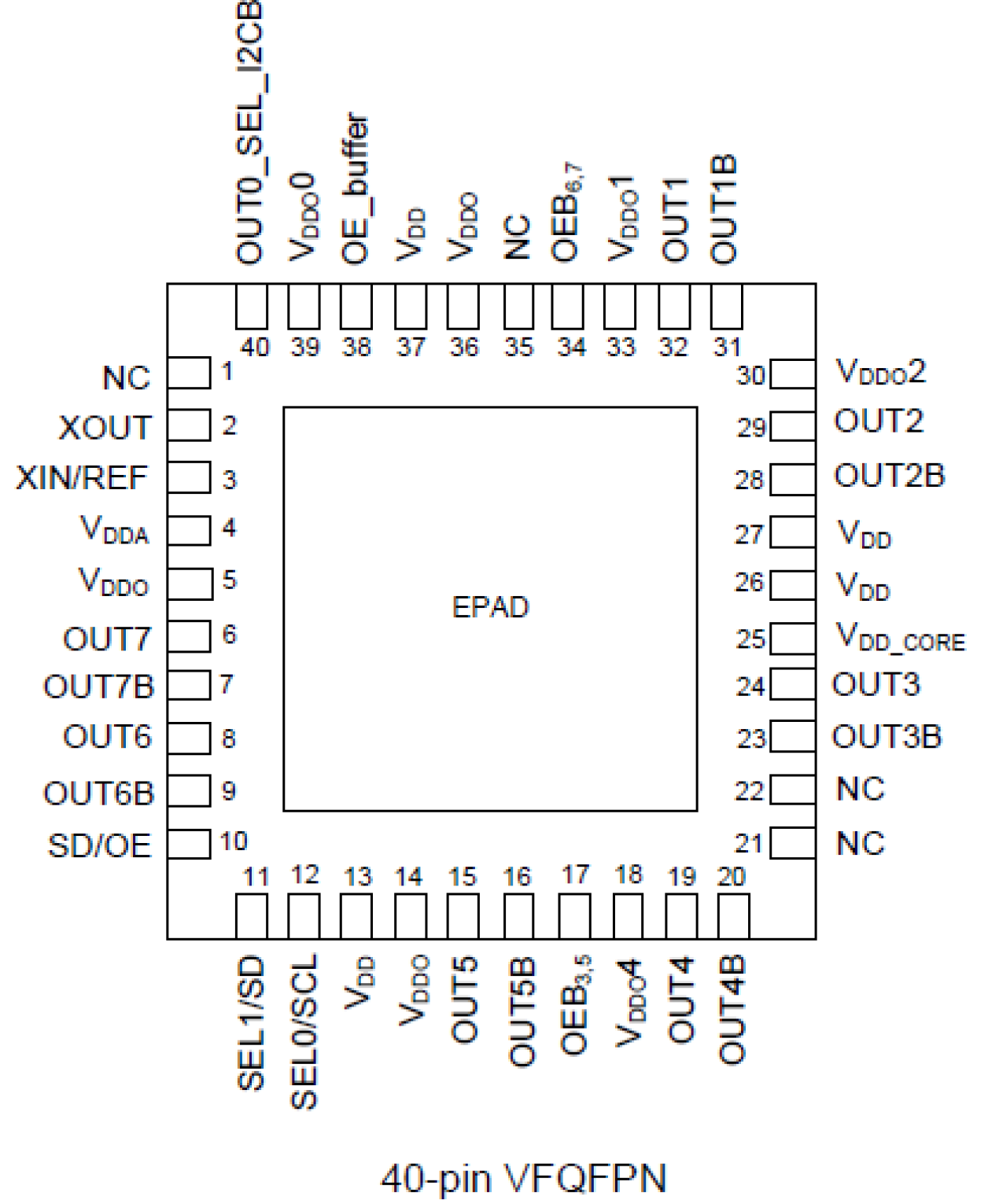

Two select pins allow up to four different configurations to be programmed and accessible using processor GPIOs or bootstrapping. The different selections may be used for different operating modes (full function, partial function, partial power down), regional standards (US, Japan, Europe), or system production margin testing. The device may be configured to use one of two I2C addresses to allow multiple devices to be used in a system. The device is packaged in a 40-pin 5mm x 5mm VFQFPN (NDG40), with an industrial operating temperature of -40 °C to +85 °C.

Applications

- Ethernet switch/router

- PCI Express 1.0/2.0/3.0

- Broadcast video/audio timing

- Multi-function printer

- Processor and FPGA clocking

- Any-frequency clock conversion

- MSAN/DSLAM/PON

- Fiber Channel, SAN

- Telecom line cards

- 1GbE and 10GbE

Applied Filters: