Features

- Lead-free packaging (Pb-free)

- Low jitter (typical 27 ps short term jitter)

- Wide input frequency range

- 8 kHz to 100 MHz

- LVCMOS single-ended clock outputs

- Up to 110 MHz

- Uses 3.3 V power supply

- 5 Volt tolerant Inputs (HSYNC, VSYNC)

- Coast (ignore HSYNC) capability via VSYNC pin

- Industry standard I2C-bus programming interface

- PLL Lock detection via I2C or LOCK output pin

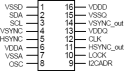

- 16-pin TSSOP package

Description

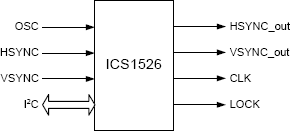

The 1526 is a low-cost, high-performance frequency generator. It is suited to general purpose phase controlled clock synthesis as well as line-locked and genlocked high-resolution video applications. Using IDT's advanced low-voltage CMOS mixed-mode technology, the 1526 is an effective clock synthesizer that supports video projectors and displays at resolutions from VGA to beyond XGA. The 1526 offers single-ended clock outputs to 110 MHz. The HSYNC_out, and VSYNC_out pins provide the regenerated versions of the HSYNC and VSYNC inputs synchronous to the CLK output. The advanced PLL uses its internal programmable feedback divider. The device is programmed by a standard I2C-bus™ serial interface and is available in a TSSOP16 package.

Applied Filters:

Loading