Features

- Cycle-to-cycle jitter <50ps

- Output-to-output skew < 65 ps

- Input-to-output delay variation <50ps

- PCIe Gen3 phase jitter < 1.0ps RMS

- QPI 9.6GT/s 12UI phase jitter < 0.2ps RMS

- Space-saving 64-pin packages

- Fixed feedback path/ 0ps input-to-output delay

- 9 Selectable SMBus Addresses/Multiple devices can share the same SMBus Segment

- 12 OE# pins/Hardware control of each output

- PLL or bypass mode/PLL can dejitter incoming clock

- 100MHz or 133MHz PLL mode operation/supports PCIe and QPI applications

- Selectable PLL bandwidth/minimizes jitter peaking in downstream PLL's

- Spread Spectrum Compatible/tracks spreading input clock for low EMI

- Software control of PLL Bandwidth and Bypass Settings/ PLL can dejitter incoming clock (B Rev only)

Description

The IDT9ZX21201 is a 12-output DB1200Z suitable for PCI Express® Gen3 or QPI applications. The part is backwards compatible to PCIe Gen1 and Gen2. A fixed external feedback maintains low drift for critical QPI applications. In bypass mode, the IDT9ZX21201 can provide outputs up to 150MHz.

Parameters

| Attributes | Value |

|---|---|

| Diff. Outputs | 12 |

| Diff. Output Signaling | HCSL |

| Output Freq Range (MHz) | 33 - 150 |

| Diff. Inputs | 1 |

| Diff. Input Signaling | HCSL |

| Accepts Spread Spec Input | Yes |

| Power Consumption Typ (mW) | 858 |

| Supply Voltage (V) | 3.3 - 3.3 |

| Output Type | HCSL |

| Diff. Termination Resistors | 52 |

| Package Area (mm²) | 81 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 33 - 150 |

| Function | Buffer |

| Input Type | HCSL |

| Output Banks (#) | 1 |

| Core Voltage (V) | 3.3 |

| Output Voltage (V) | 0.7 |

| Product Category | Processor Clock Buffers, Zero Delay Buffers |

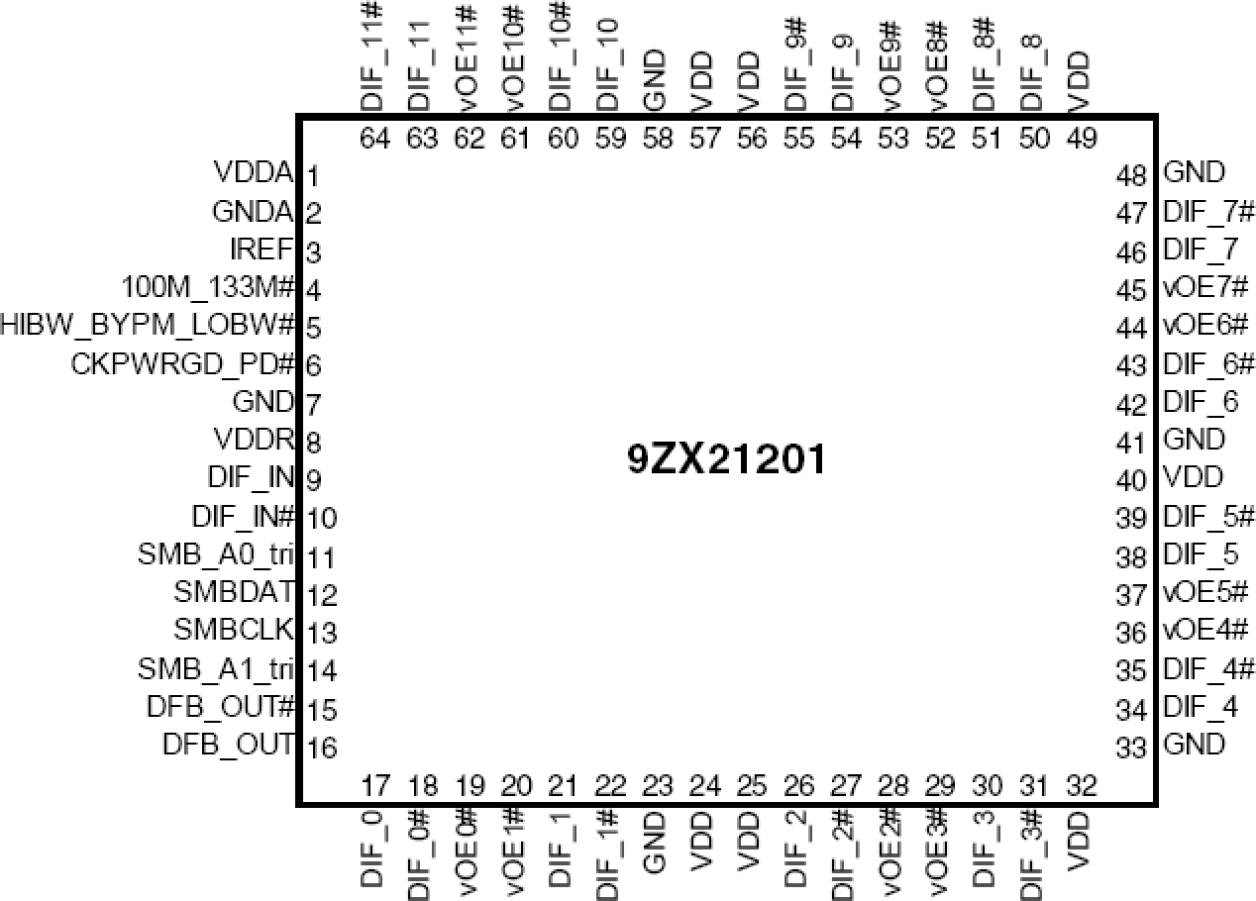

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 9.0 x 9.0 x 0.9 | 64 | 0.5 |

Applied Filters: