特長

- 64bit RISC-V/AX45MP(シングル)

- DDR4あるいはDDR3Lの外部メモリインタフェース

- メモリの誤り検出・訂正(ECC)機能

- ギガビットイーサネット2ch

- CANインタフェース(CAN-FD)2ch

- USB2.0インタフェース 2ch

- SDインタフェース 2ch

- ADコンバータ 2ch

- 13 x 13mm BGAパッケージ、11x11mm BGAパッケージ

- RZファミリMPUの検証済みDRAMオプションはこちら

説明

RZ/FiveマイクロプロセッサはRISC-V CPU(AX45MP Single)1.0 GHz、16ビットDDR3L/DDR4 インタフェースを内蔵しています。また、 Gbit-Ether 、CAN、及び、USB 2.0などの多くのインターフェースも備えており、エントリークラスの社会インフラ用途ゲートウエイ制御機器や産業用途ゲートウエイ制御機器などのアプリケーションに最適です。

RZ/Fiveは2つのパッケージオプションがあります。

13 x 13 mm Package Part Number: R9A07G043F01GBG#BC0

11 x 11 mm Package Part Number: R9A07G043F00GBG#BC0

また、RZ/Five 13 x 13 mm Packageは、RZ/G2UL(Type1)とピン互換です。

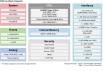

パラメータ

| 属性 | 値 |

|---|---|

| CPU Architecture | RISC-V |

| Main CPU | RISC-V (AX45MP Single) |

| Program Memory (KB) | 0 |

| RAM (KB) | 128 |

| Carrier Type | Bulk (Tray), Full Carton (Tray) |

| Supply Voltage (V) | 2.97 - 3.63 |

| I/O Ports | 65, 114 |

| NPU | No |

| DRAM I/F | DDR3L-1333, DDR4-1600 (16-bit) |

| 3D GPU | No |

| Temp. Range (°C) | Ta = -40 to +85 |

| Operating Freq (Max) (MHz) | 1000 |

| Ethernet speed | 10M/100M/1G |

| Ethernet (ch) | 1, 2 |

| EtherCat (ch) (#) | 0 |

| USB FS (host ch/device ch) | ( 2 / 2 ) |

| USB HS (host ch/device ch) | ( 2 / 2 ) |

| USB SS (host ch/device ch) | ( 0 / 0 ) |

| PCI Express (generation and ch) | No |

| SCI or UART (ch) | 7 |

| SPI (ch) | 3 |

| I2C (#) | 4 |

| CAN (ch) | 2 |

| CAN-FD (ch) | 2 |

| Wireless | No |

| SDHI (ch) | 2 |

| High Resolution Output Timer | No |

| PWM Output (pin#) | 0 |

| 32-Bit Timer (ch) | 4 |

| 16-Bit Timer (ch) (#) | 8 |

| 8-Bit Timer (ch) | 0 |

| Standby operable timer | No |

| Asynchronous General Purpose Timer / Interval Timer (ch) | 0 |

| 16-Bit A/D Converter (ch) | 0 |

| 14-Bit A/D Converter (ch) | 0 |

| 12-Bit A/D Converter (ch) | 2 |

| 10-Bit A/D Converter (ch) | 0 |

| 24-Bit Sigma-Delta A/D Converter (ch) | 0 |

| 16-Bit D/A Converter (ch) | 0 |

| 12-Bit D/A Converter (ch) | 0 |

| 10-Bit D/A Converter (ch) (#) | 0 |

| 8-Bit D/A Converter (ch) | 0 |

| Capacitive Touch Sensing Unit (ch) | 0 |

| Graphics LCD Controller | No |

| MIPI Interfaces (DSI) (ch) | 0 |

| MIPI Interfaces (CSI) (ch) | 0 |

| Image Codec | No |

| Segment LCD Controller | No |

| Security & Encryption | No, Secure boot,AES,RSA,ECC,Hash,TRNG |

製品比較

| RZ/Five | RZ/G2UL | |

| CPU | RISC-V (AX45MP Single) | Cortex-A55 x 1 + Cortex-M33 x 1 |

| Lead Count (#) | 266, 361 | 361 |

| Operating Freq (Max) (MHz) | 1000 | 1000 |

| Ethernet Remarks | Gigabit Ethernet: 2ch or 1ch | Gigabit Ethernet: 2ch or 1ch |

| CAN (ch) | 2 | 2 |

| Display Function Remarks | Display Function: No | Parallel Interface |

アプリケーション・ブロック図

| エントリークラスのHMIプラットフォーム エントリークラスのプラットフォームで、最新のHMIディスプレイ向けに信頼性の高い64ビット性能を提供します。 |

その他アプリケーション

- IoTゲートウエイ

- 産業用途ゲートウエイ

適用されたフィルター