パッケージ情報

| CADモデル: | View CAD Model |

| Pkg. Type: | FCCSP |

| Pkg. Code: | AVG240 |

| Lead Count (#): | 240 |

| Pkg. Dimensions (mm): | 13.5 x 8.7 x 0.9 |

| Pitch (mm): | 0.65 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | |

| HTS (US) |

製品スペック

| Pkg. Type | FCCSP |

| Lead Count (#) | 240 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 170 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e1 SnAgCu |

| Temp. Range (°C) | 0 to 70°C |

| Function | DDR5 Gen 2.0 Server RCD |

| Input Voltage Range (V) | 1.06 - 1.16 |

| Length (mm) | 13.5 |

| MOQ | 170 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 13.5 x 8.7 x 0.9 |

| Supply Voltage (V) | 1.06 - 1.16 |

| Tape & Reel | No |

| Thickness (mm) | 0.9 |

| Width (mm) | 8.7 |

| 掲載 | No |

RG5R256 に関するリソース

説明

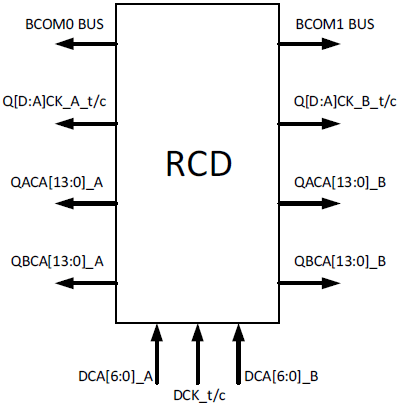

The RG5R256 (Gen 2 RCD) is a registering clock driver used on DDR5 RDIMMs, LRDIMMs and NVDIMMs. It supports DDR5 server speeds up to 5600 MT/s. Its primary function is to buffer the Command Address (CA) bus, chip selects, and clock between the host controller and the DRAMs. It also creates a BCOM bus to control the data buffers for LRDIMMs.

The RG5R256 contains two separate channels with some common logic such as clocking, but otherwise operate independently of each other. Each channel has a 7-bit double data rate CA bus input, a single parity input, two chip-select inputs, produces two copies of 14-bit single data rate CA bus outputs and two copies of the chip-select outputs. The RCD has a common clock input and PLL, but produces separate clock outputs to the DRAM channels.