パッケージ情報

| CADモデル: | View CAD Model |

| Pkg. Type: | PDIP |

| Pkg. Code: | EUL |

| Lead Count (#): | 8 |

| Pkg. Dimensions (mm): | 9.65 x 6.60 x 3.94 |

| Pitch (mm): | 2.54 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pb (Lead) Free | No |

| ECCN (US) | |

| HTS (US) |

製品スペック

| Lead Count (#) | 8 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pitch (mm) | 2.5 |

| Pkg. Dimensions (mm) | 9.7 x 6.6 x 3.94 |

| Pb (Lead) Free | No |

| Pb Free Category | Hot Solder Dip/Solder Plate Comm. PDIP ONLY |

| Temp. Range (°C) | 0 to +70°C |

| IOUT (Max) (mA) | 20 |

| IS (Typical) | 170 |

| IS (mA) | 0.5 |

| Input Voltage (Max) (V) | 10 |

| Input Voltage (Min) (V) | 1.5 |

| Length (mm) | 9.7 |

| Longevity | 2033 12月 |

| MOQ | 3000 |

| Output Voltage (Max) (V) | -10 |

| Output Voltage (Min) (V) | -1.5 |

| Parametric Category | Charge Pumps (Inductorless) |

| Pkg. Type | PDIP |

| Qualification Level | Standard |

| Switching Frequency Range (Typical) (kHz) | 10 - 10 |

| Thickness (mm) | 3.94 |

| Width (mm) | 6.6 |

ICL7660 に関するリソース

説明

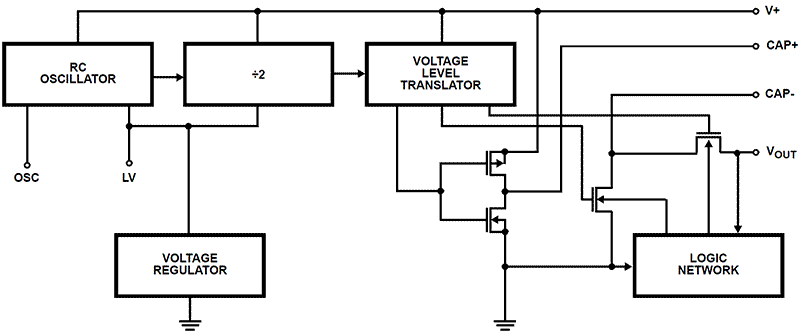

The Intersil ICL7660 and ICL7660A are monolithic CMOS power supply circuits which offer unique performance advantages over previously available devices. The ICL7660 performs supply voltage conversions from positive to negative for an input range of +1.5V to +10.0V resulting in complementary output voltages of -1.5V to -10.0V and the ICL7660A does the same conversions with an input range of +1.5V to +12.0V resulting in complementary output voltages of -1.5V to -12.0V. Only 2 noncritical external capacitors are needed for the charge pump and charge reservoir functions. The ICL7660 and ICL7660A can also be connected to function as voltage doublers and will generate output voltages up to +18.6V with a +10V input. Contained on the chip are a series DC supply regulator, RC oscillator, voltage level translator, and four output power MOS switches. A unique logic element senses the most negative voltage in the device and ensures that the output N-channel switch source-substrate junctions are not forward biased. This assures latchup free operation. The oscillator, when unloaded, oscillates at a nominal frequency of 10kHz for an input supply voltage of 5.0V. This frequency can be lowered by the addition of an external capacitor to the OSC terminal, or the oscillator may be overdriven by an external clock. The LV terminal may be tied to GROUND to bypass the internal series regulator and improve low voltage (LV) operation. At medium to high voltages (+3.5V to +10.0V for the ICL7660 and +3.5V to +12.0V for the ICL7660A), the LV pin is left floating to prevent device latchup.