概要

説明

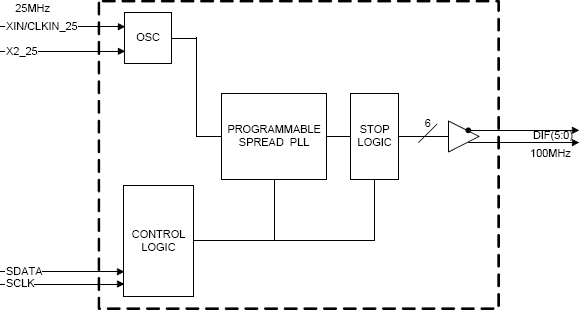

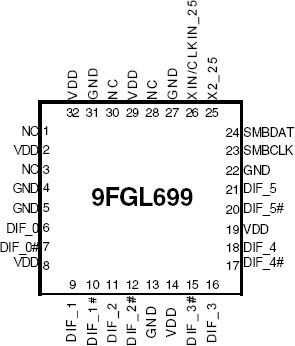

The 9FGL699 is a 6-output low-power clock sythesizer for PCIe Gen2. It runs from a 25 MHz XTAL, provides spread spectrum capability, and has an SMBus for software control of the device.

特長

- 6 - 100 MHz Differential low power push pull (HCSL compatible) output pairs

- 32-pin QFN; space-savings

- Push Pull outputs

- Low power consumption, reduced component count

- PCIe Gen2

- Spread spectrum capability; reduced EMI when needed

- D2/D3 SMBus Write/Read SMBus address

- Cycle-to-cycle jitter <125 ps

- Output-to-output skew < 100 ps

- Current consumption < 40 mA

- PCIe Gen2 phase jitter < 3.0 ps RMS

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

サポート

ビデオ&トレーニング

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

Watch the Video Series Below