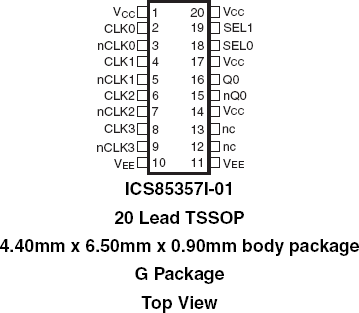

パッケージ情報

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 6.5 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Lead Count (#) | 20 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 3000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Core Voltage (V) | 3.3 |

| Function | Multiplexer |

| Input Freq (MHz) | 750 |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 4 |

| Length (mm) | 6.5 |

| MOQ | 2500 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 750 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 1 |

| Package Area (mm²) | 28.6 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 6.5 x 4.4 x 1.0 |

| Pkg. Type | TSSOP |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

| 掲載 | No |

85357I-01 に関するリソース

説明

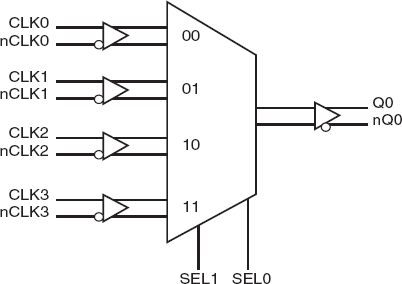

The 85357I-01 is a 4:1 or 2:1 Differential-to-3.3V LVPECL / ECL clock multiplexer which can operate up to 750MHz. The 85357I-01 has 4 selectable clock inputs. The CLK, nCLK pair can accept most standard differential input levels. The device can operate using a 3.3V LVPECL (VEE = 0V, VCC = 3.135V to 3.465V) or 3.3V ECL (VCC = 0V, VEE = -3.135V to -3.465V). The fully differential architecture and low propagation delay make it ideal for use in clock distribution circuits. The select pins have internal pulldown resistors. Leaving one input unconnected (pulled to logic low by the internal resistor) will transform the device into a 2:1 multiplexer. The SEL1 pin is the most significant bit and the binary number applied to the select pins will select the same numbered data input (i.e., 00 selects CLK0, nCLK0).