パッケージ情報

| CADモデル: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | ESG48 |

| Lead Count (#): | 48 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.5 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Lead Count (#) | 48 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 250 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Advanced Features | Programmable Clock |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 19 - 622 |

| Input Type | LVPECL |

| Inputs (#) | 3 |

| Length (mm) | 7 |

| MOQ | 250 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 1244.16 - 1244.16, 622.08 - 622.08, 311.04 - 311.04, 155.52 - 155.52, 77.76 - 77.76, 38.88 - 38.88 |

| Output Signaling | LVPECL |

| Output Skew (ps) | 200 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 6 |

| Package Area (mm²) | 49 |

| Pitch (mm) | 0.5 |

| Pkg. Type | TQFP |

| Prog. Clock | Yes |

| Prog. Interface | Parallel |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | No |

| Thickness (mm) | 1.4 |

| VCO Max Freq (MHz) | 662 |

| VCO Min Freq (MHz) | 560 |

| Width (mm) | 7 |

| 掲載 | No |

843S06 に関するリソース

説明

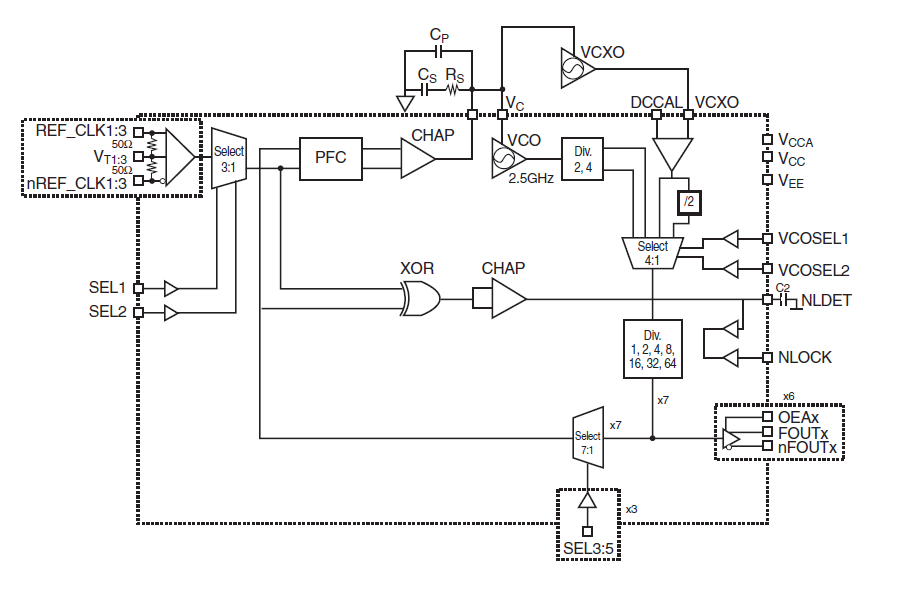

The 843S06 is a low voltage, low skew 3.3V LVPECL Clock Synthesizer. The device targets clock distribution in SDH/SONET telecommunication systems but is well suited for a wide range of applications requiring high performance high-speed clock synthesis. The device implements a fully integrated multiplying PLL including: