特長

- High-voltage type (20V rating)

- 5V, 10V and 15V parametric ratings

- Standardized, symmetrical output characteristics

- 100% tested for quiescent current at 20V

- Maximum input current of 1µA at 18V over full package temperature range, 100nA at 18V and +25 °C

- Noise margin (over full package temperature range): 1V at VDD = 5V, 2V at VDD = 10V, 2.5V at VDD = 15V

- Meets all requirements of JEDEC tentative standard No. 13A, "Standard Specifications for Description of 'B' Series CMOS Devices"

説明

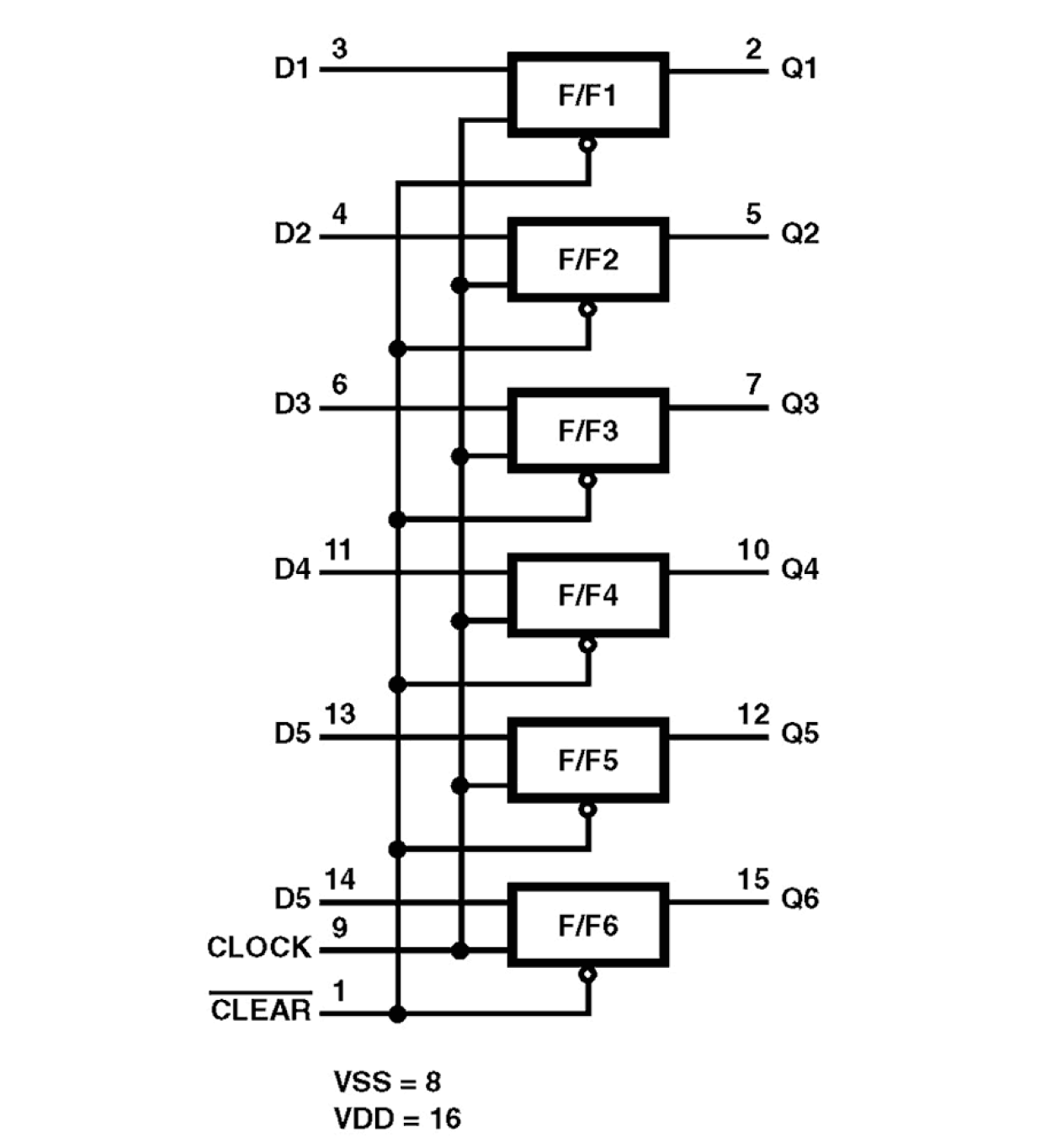

The CD40174BMS consists of six identical D-Type flip-flops having independent data inputs. The clock and clear inputs are common to all six units. Data is transferred to the Q outputs on the positive-going transition of the clock pulse. All six flip-flops are simultaneously reset by a low level on the CLEAR input. The CD40174BMS is supplied in these 16-lead outline packages: Braze Seal DIP H4T, Frit Seal DIP H1E and Ceramic Flatpack H6W.

アプリケーション

- Shift registers

- Buffer/Storage registers

- Pattern generators

適用されたフィルター