Features

- PCIe Gen1–4 compliant

- LP-HCSL outputs with integrated terminations; save 24 resistors compared to standard PCIe devices

- 54 mW typical power consumption; reduced thermal concerns

- Outputs can optionally be supplied from any voltage between 1.05 and 1.8V; maximum power savings

- OE# pins; support DIF power management

- Programmable slew rate for each output; allows tuning for various line lengths

- Programmable output amplitude; allows tuning for various application environments

- DIF outputs blocked until PLL is locked; clean system start-up

- Selectable 0%, -0.25% or -0.5% spread on DIF outputs; reduces EMI

- External 25 MHz crystal; supports tight ppm with 0 ppm synthesis error

- Configuration can be accomplished with strapping pins; SMBus interface not required for device control

- 3.3 V tolerant SMBus interface works with legacy controllers

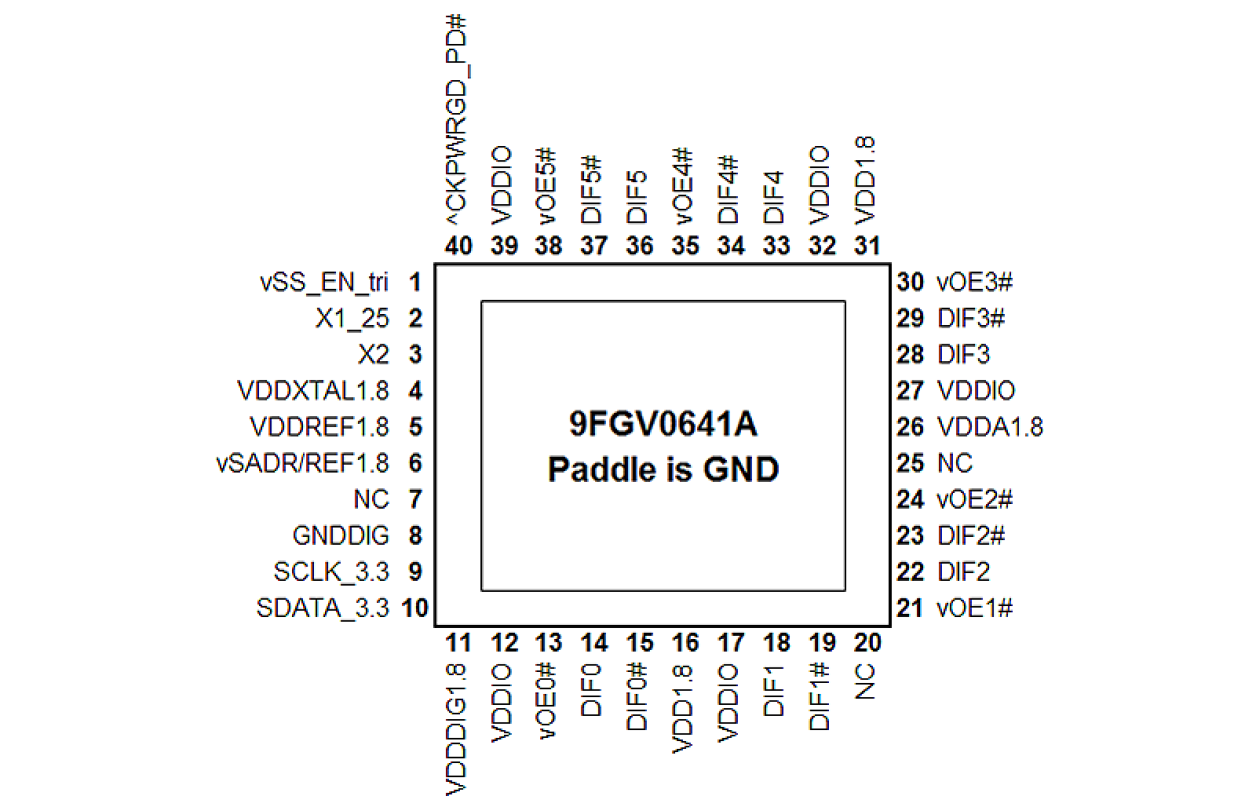

- Space saving 5x5 mm 40-pin VFQFPN; minimal board space

- Selectable SMBus addresses; multiple devices can easily share an SMBus segment

Description

The 9FGV0641 is a member of IDT's SOC-Friendly 1.8V Very-Low-Power PCIe clock family. The device has integrated 100 ohm output terminations providing direction connection to 100 ohm transmission lines. The device also has 6 output enables for clock management and supports 2 different spread spectrum levels in addition to spread off.

For information regarding evaluation boards and material, please contact your local IDT sales representative.

Parameters

| Attributes | Value |

|---|---|

| Diff. Outputs | 6 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 25 - 25, 100 - 100 |

| Power Consumption Typ (mW) | 54 |

| Supply Voltage (V) | 1.8 - 1.8 |

| Output Type | LP-HCSL, LVCMOS |

| Xtal Freq (MHz) | 25 - 25 |

| Diff. Termination Resistors | 0 |

| Package Area (mm²) | 25 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 25 - 25 |

| Function | Generator |

| Input Type | Crystal, LVCMOS |

| Core Voltage (V) | 1.8 |

| Output Voltage (V) | 0.8V, 1.8V |

| Product Category | PCI Express Clocks |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 5.0 x 5.0 x 0.9 | 40 | 0.4 |

Application Block Diagrams

| Scalable HMI SMARC SoM with AI Scalable SoM with multi-core processing, advanced graphics, and robust connectivity for smart HMI. |

| High-Performance Human Machine Interface (HMI) System Versatile system on module (SoM) for driving a wide range of human machine interface capabilities. |

| Multi-Display HMI SoM SOM with optimized power and timing supports multi-display embedded applications. |

Applied Filters: