Features

- Logic and Mixed Signal Circuits

- Highly Versatile Macrocells

- Read Back Protection (Read Lock)

- 1.8V (±5%) to 5V (±10%) VDD

- 1.8V (±5%) to 5V (±10%) VDD2 (VDD2 ≤ VDD)

- Operating Temperature Range: -40°C to 85°C

- RoHS-Compliant/Halogen-Free

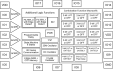

- Macrocells Overview

- Four Analog Comparators (ACMP)

- Two Voltage References (Vref)

- Nineteen Combination Function Macrocells

- Three Selectable DFF/Latch or 2-bit LUTs

- One Selectable Continuous DFF/Latch or 3-bit LUT

- Four Selectable DFF/Latch or 3-bit LUTs

- One Selectable Pipe Delay or 3-bit LUT

- One Selectable Programmable Function Generator or 2-bit LUT

- Five 8-bit Delays/Counters or 3-bit LUTs

- Two 16-bit Delays/Counters or 4-bit LUTs

- Two Deglitch Filters with Edge Detectors

- State Machine

- Eight States

- Flexible Input Logic from State Transitions

- Serial Communications

- I2C Protocol Compliant

- Pipe Delay – 16 Stage/3 Output (Part of Combination Function Macrocell)

- Programmable Delay

- One Inverter

- Two Oscillators (OSC)

- Configurable 25kHz/2MHz

- 25MHz RC Oscillator

- Crystal Oscillator

- Power-On Reset (POR)

- Eight-Byte RAM + OTP User Memory

- RAM Memory Space that is Readable and Writable via I2C

- User-defined Initial Values Transferred from OTP

Description

The SLG46538 programmable mixed-signal matrix with asynchronous state machine and dual supply provides a small, low-power component for mixed-signal functions. The user creates their circuit design by programming the one-time programmable (OTP) non-volatile memory (NVM) to configure the interconnect logic, the I/O pins, and the macrocells of the SLG46538. This highly versatile device allows for a wide variety of mixed-signal functions to be designed within a very small, low-power single integrated circuit. The additional power supply (VDD2) on the SLG46538 provides the ability to interface two independent voltage domains within the same design. Users can configure pins, dedicated to each power supply, as inputs, outputs, or both (controlled dynamically by internal logic) to both VDD and VDD2 voltage domains. Using the available macrocells, designers can implement mixed-signal functions bridging both domains or simply pass through level translation in both High to Low and Low to High directions.

Parameters

| Attributes | Value |

|---|---|

| Nominal VDD | 1.71 - 5.5 |

| VDD2 (V) | 1.71 - 5.5 |

| GPIOs (#) | 16, 17 |

| Special Features | ASM (8 states) |

| ACMP Channels (#) | 4 |

| CNT/DLY (Max) (#) | 7 |

| LUTs (Max) (#) | 17 |

| DFF (Max) (#) | 8 |

| Pipe Delay | 16-stage |

| # of Programable Delays (#) | 1 |

| Oscillator Type | Conf. OSC, RC OSC, Crystal OSC, Conf. OSC, Ring OSC, Crystal OSC |

| Temperature Sensor (ch) (#) | 1 |

| Interface | I2C |

| Memory Type | OTP |

| Temp. Range (°C) | -40 to +85°C |

Application Block Diagrams

|

Low-Cost Smart Instrument Cluster

Low-cost smart instrument cluster with single-chip design for efficient, custom LCD bike and vehicle displays.

|

|

Level 2 EV Charger

Modular EVSE system with advanced connectivity for efficient EV charging and management.

|

|

48V/3kW Motor Control for 2/3 Wheelers

The 48V/3kW motor control system features a scalable inverter design, phase overcurrent fault detection, and ASIL-B safety.

|

|

Robot Vacuum Cleaner

This smart robot vacuum features environment mapping, anti-drop, obstacle detection, auto-recharge, app control.

|

|

Scalable SMARC 2.1 Gateway SoM with RISC-V MPU

The scalable SMARC 2.1 SoM design for IIoT gateways with low power consumption, strong connectivity, and flexibility.

|

|

RTOS-Based RZ/A3UL HMI SMARC SoM

SOM with optimized power for low-power and real-time HMI control in smart buildings.

|

|

SMARC System for Single-Core Arm Cortex-A55 MPU

AI-ready SMARC SoM with Arm Cortex-A55 MPU for low-power HMI and industrial control.

|

Additional Applications

- Personal Computers and Servers

- PC Peripherals

- Consumer Electronics

- Data Communications Equipment

- Handheld and Portable Electronics