Overview

Description

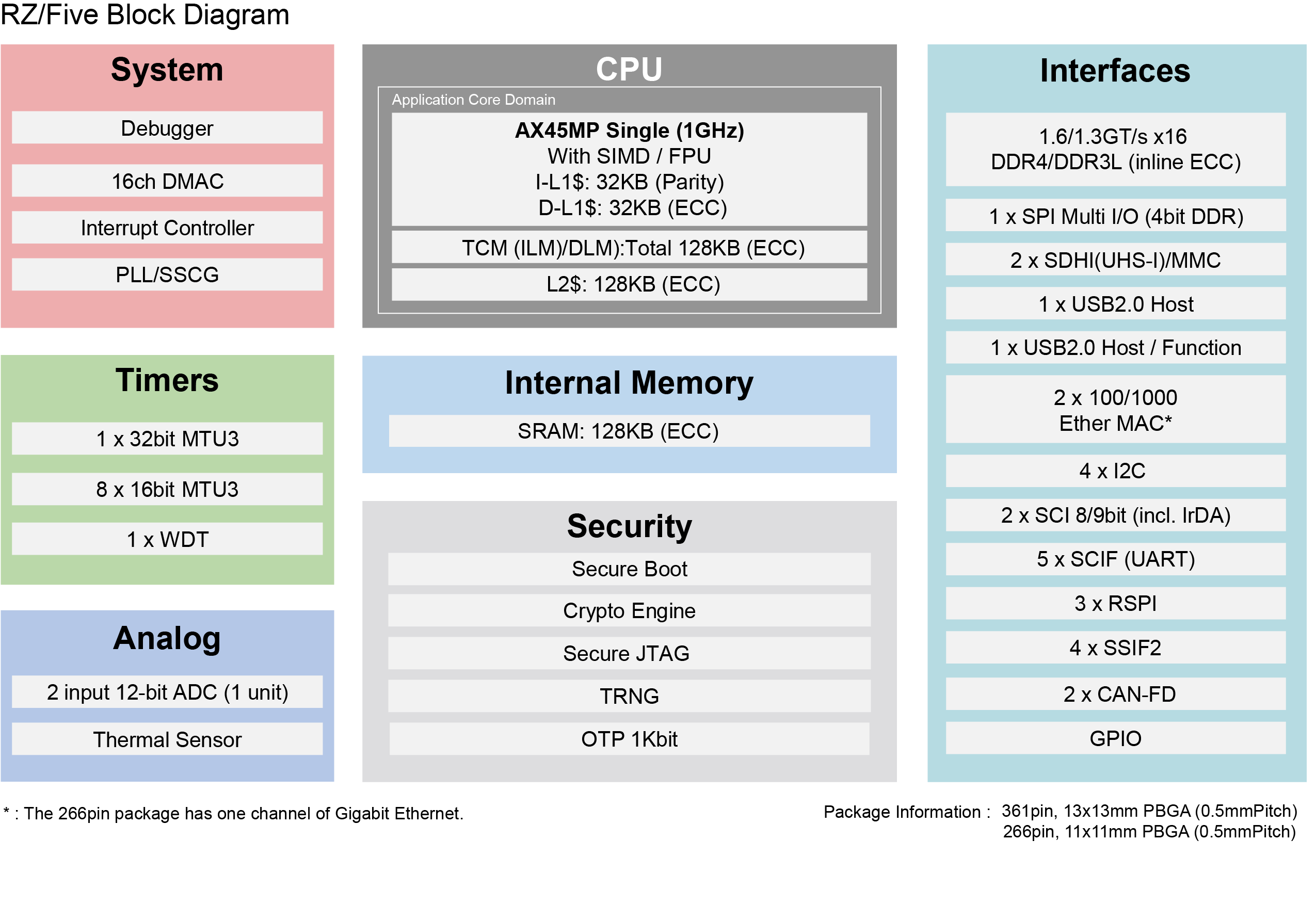

The RZ/Five microprocessor includes a RISC-V CPU Core (AX45MP Single) 1.0 GHz, 16-bit DDR3L/DDR4 interface. And it also has many interfaces such as Gbit-Ether, CAN, and USB 2.0, making it ideal for applications such as entry-class social infrastructure gateway control and industrial gateway control.

There are two package options. Please refer to the RZ/Five Overview for the differences in the functions supported by each.

13 x 13 mm Package Part Number: R9A07G043F01GBG#BC0

11 x 11 mm Package Part Number: R9A07G043F00GBG#BC0

The RZ/Five 13 x 13 mm package is also pin compatible with the RZ/G2UL (Type 1).

Features

- 64-bit RISC-V/AX45MP (Single)

- DDR4 or DDR3L memory interface

- Memory error detection / correction (ECC)

- Gigabit Ethernet 2ch

- CAN interface (CAN-FD) 2ch

- USB 2.0 interface 2ch

- SD interface 2ch

- AD converter 2ch

- 13 x 13mm BGA package、11x11mm BGA package

Comparison

Applications

Design & Development

Software & Tools

Boards & Kits

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Support

Support Communities

Support Communities

-

RZ/Five gcc issue

Dear Renesas Team, I have enabled GCC in RZ/Five and RZ/G2L smarc board, in RZ/G2L it is working fine, but in RZ/Five it is trowing an error not able to build anything, it is showing segmentation fault. please find the below config ...

Mar 27, 2023 -

Issue in PWM enabling in RZ/Five

Hello, We are using VLP3.0.4 in RZ/Five processor. Trying to test PWM (MTU3) in RZ/Five using below commands. But PWM is not getting enabled. cd /sys/class/pwm/pwmchip0/echo 0 > exportecho 1000000 > pwm0/periodecho 500000 > pwm0/ ...

Sep 22, 2023 -

RZ/Five docker issue

Dear Renesas Team, I have built RZ/Five BSP 3.0.3 and have enabled docker, but facing this issue, please find the attached below image.

May 3, 2023

FAQs

-

RZ/Five: Maximum transfer rate of SPI (Renesas Serial Peripheral Interface)

Last Updated: 07/28/2023 Question: How much is the maximum transfer rate of RSPI (Renesas Serial Peripheral Interface)? Answer: The maximum transfer rate of RSPI is not decided only by the specifications of RZ/Five, but also depends on the specifications of the connected counter device ...

Jul 28, 2023 -

RZ/Five: What methods do the Gigabit Ethernet interface of the RZ/Five support?

Last Updated: 09/21/2022 Question: What methods do the Gigabit Ethernet interface of the RZ/Five support? Answer: MII and RGMII are supported. Suitable Products RZ/Five Go to Japanese Go to Chinese

Sep 21, 2022 -

RZ/Five: What is the vendor name and IP name of RISC-V CPU IP?

Last Updated: 09/21/2022 Question: What is the vendor name and IP name of RISC-V CPU IP? Answer: It is Andes Technology Corporation. The IP's Name is AndesCore™ AX45MP. Suitable Products RZ/Five Go to Japanese Go to Chinese

Sep 21, 2022

Videos & Training

RZ/Five provides a new platform for high-performance IoT Edge solutions. Learn the advantages of RISC-V CPU, and how to easily scale development across RISC-V and Arm cores.

Events & Webinars

News & Blog Posts

Blog Post

Jul 21, 2023

|

Blog Post

Sep 16, 2022

|

News

Mar 1, 2022

|