Overview

Description

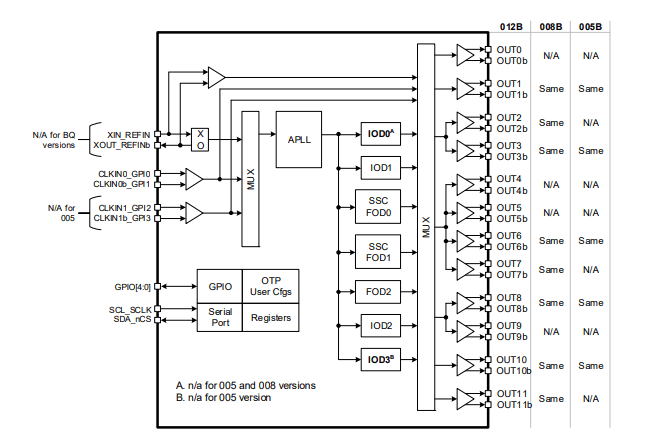

The RC21xxxB (RC21012B and RC21008B) is a member of Renesas's VersaClock® 7 programmable clock generator family. It is intended for high-performance computers, data communications, and industrial applications, designed to be placed immediately adjacent to a PHY, switch, ASIC or FPGA that requires several reference clocks with jitter performance 150fs typical RMS.

Up to 27 configurations reusable across multiple designs may be stored in on-chip One-Time Programmable (OTP) memory or external I2C EEPROM. Redundant input is available for backup and used as a reference clock where needed.

Features

- 1.8V/2.5V/3.3V flexible power rails

- Typical 150fs RMS 12kHz - 20MHz phase jitter

- 5/8/12 outputs with integrated crystal options

- 1kHz to 650MHz LVDS/LP-HCSL outputs

- 1kHz to 200MHz LVCMOS outputs

- Programmable hardware configuration select-pins

- PCIe Gen 5/6/7 ready

- Space saving packages 4mm x 4mm, 5mm x 5mm, 6mm x 6mm

- Integrated crystal option for space saving and BOM optimization

Comparison

Applications

Design & Development

Software & Tools

Boards & Kits

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Support

Support Communities

Support Communities

-

Example source code on programming RC210xx via I2C

Hi, Is there any example code on programming RC210xx via I2C from an RBS file? I tried the example mentioned in the programming guide and perform a read back of all the registers, the registers value is not the same (90%) as what I programmed. I have attached 3 files ...

Mar 4, 2025 -

RC21012B000GNA - Sharing CLKIN0 and CLKIN1 in

Dear Renesas Forum, I need to generate 100 MHz and 50 MHz, without using the APLL. Is there any way achieving this with only 1 CLK? I try to avoid an external buffer. E.g. is it possible to use only CLKIN0 with a 100 MHz LVDS CLK and share ...

Jul 7, 2025 -

Timing Personalitt file (.tcp) for RC21008x

Hello I am trying to configure the RC21008a frequency synthesizer on the Versal Eval Board VEK280 from AMD. I want to use the IDT Timing Commader to get the right config values. Where do I file the right tcp file to do the same? Thanks Kedhar

Jul 9, 2025

Videos & Training

Learn more about how to configure the VersaClock®7 evaluation board using the supporting RICBox software. VersaClock®7 devices achieve any frequency-in, any frequency-out for high speed SerDes used in switches routers, accelerator cards, and server applications.

News & Blog Posts

Blog Post

Jul 17, 2025

|

Blog Post

Apr 14, 2022

|

Blog Post

May 22, 2018

|

News

Apr 30, 2018

|