Overview

Description

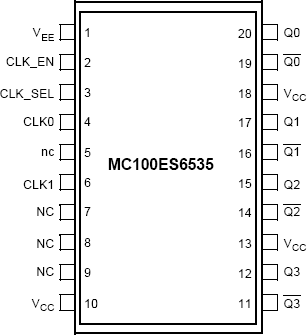

The MC100ES6535 is a low skew, high performance 3.3 V 1-to-4 LVCMOS to LVPECL fanout buffer. The ES6535 has two selectable inputs that allow LVCMOS or LVTTL input levels which translate to LVPECL outputs. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin. The ES6535 is ideal for high performance clock distribution applications.

Features

- 4 differential LVPECL outputs

- 2 selectable LVCMOS/LVTTL inputs

- 1 GHz maximum output frequency

- Translates LVCMOS/LVTTL levels to LVPECL levels

- 30 ps maximum output skew

- 190 ps part-to-part skew

- 3.3 V operating range

- 20-lead TSSOP package

- Ambient temperature range –40°C to +85°C

- 20-lead Pb-free package available

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters:

Support

Support Communities

Get quick technical support online from Renesas Engineering Community technical staff.