Features

- LP-HCSL outputs; save 4 resistors compared to standard HCSL outputs.

- 35 mW typical power consumption in PLL mode; minimal power consumption

- OE# pins; support DIF power management

- HCSL-compatible differential input; can be driven by common clock sources

- LP-HCSL differential clock outputs; reduced power and board space

- Programmable slew rate for each output; allows tuning for various line lengths

- Programmable output amplitude; allows tuning for various application environments

- Pin/software selectable PLL bandwidth and PLL Bypass; minimize phase jitter for each application

- Outputs blocked until PLL is locked; clean system start-up

- Configuration can be accomplished with strapping pins; SMBus interface not required for device control.

- 3.3 V tolerant SMBus interface works with legacy controllers

- Space-saving 4x4 mm 24-pin VFQFPN; minimal board space

Description

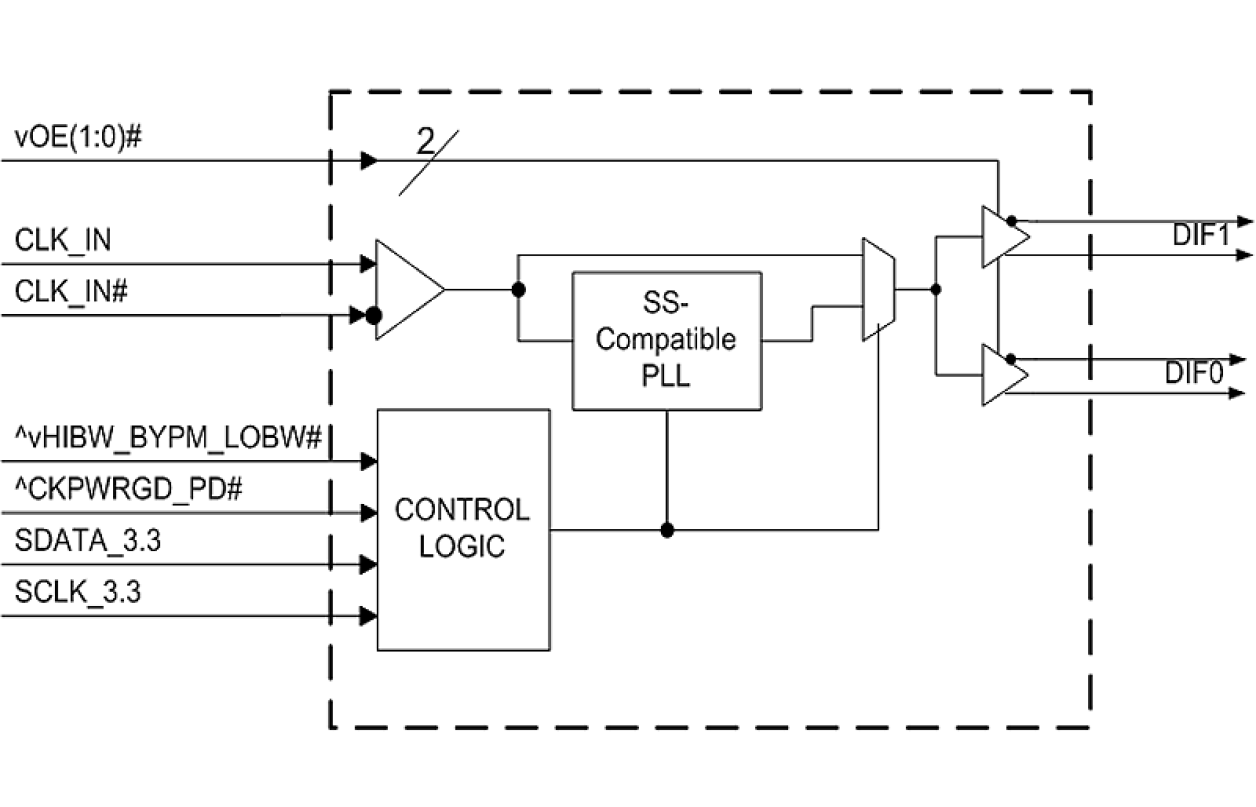

The 9DBU0231 is a member of IDT's 1.5 V Ultra-Low-Power (ULP) PCIe family. The device has 2 output enables for clock management.

Parameters

| Attributes | Value |

|---|---|

| Diff. Outputs | 2 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 1 - 167 |

| Diff. Inputs | 1 |

| Diff. Input Signaling | HCSL |

| Accepts Spread Spec Input | Yes |

| Power Consumption Typ (mW) | 35 |

| Supply Voltage (V) | 1.5 - 1.5 |

| Output Type | LP-HCSL |

| Package Area (mm²) | 16 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Input Freq (MHz) | 30 - 175 |

| Additive Phase Jitter Typ RMS (fs) | 313 |

| Function | Zero Delay Buffer |

| Input Type | HCSL |

| Output Banks (#) | 1 |

| Core Voltage (V) | 1.5 |

| Output Voltage (V) | 0.8 |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 4.0 x 4.0 x 0.9 | 24 | 0.5 |

Applied Filters:

Filters

Software & Tools

Sample Code

Simulation Models

A detailed overview of IDT's full-featured PCI Express (PCIe) clock and timing solutions. The presentation addresses PCIe Gen 1, Gen 2, Gen 3, and Gen 4 architectures and how IDT's industry-leading solutions provide all the functions, features, and performance required by the application.

Presented by Ron Wade, System Architect at IDT. For more information visit the PCIe clocks page.

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

In this episode, Ron Wade from IDT (acquired by Renesas) explains PCIe common clocking and its impact on timing solutions. Learn about using a single clock source, fan-out buffers, and the considerations for spread spectrum and non-spread spectrum clocking in PCIe systems.

In this video, we explore PCIe with separate reference clocks and the effects of clock selection. Learn how separate reference clocks work and their impact on system performance and stability.

This video provides a high-level overview of Separate Reference Clock with Independent Spread (SRIS) architectures for PCI Express systems, additional performance requirements that this clocking architecture imposes on the reference clocks, and some system implications encountered trying to implement the architecture.

IDT (acquired by Renesas) engineer provides a brief tutorial describing the main differences between standard HCSL and low-power HCSL (LP-HCSL).

Presented by Ron Wade, PCI Express timing expert.

Related Resources

IDT (acquired by Renesas) engineer provides a brief tutorial on why zero delay buffers (ZDBs) are offered with two different bandwidths (1 MHz and 3 MHz). The reason has to do with jitter peaking when cascading PLLs.

Presented by Ron Wade, PCI Express timing expert.

Related Resources

An overview of IDT's full-featured PCI Express (PCIe) clock zero-delay buffers and fanout buffers addressing PCIe Gen 1, Gen 2, Gen 3, and Gen 4.

Presented by Ron Wade, System Architect at IDT.

An overview of PCI Express applications and how IDT's industry-leading portfolio of PCIe clock products addresses the requirements. The video briefly discusses PCIe riser cards, embedded SOC, and PCIe storage (NVME) examples.

Presented by Ron Wade, System Architect at IDT.

A brief overview of how data rates have changed from PCI Express (PCIe) Generation 1, Gen 2, Gen 3, Gen 4 and Gen 5.

Presented by Ron Wade, system architect at IDT. For more information about IDT's PCIe timing solutions, visit the PCI Express (PCIe) Clocks page.

A brief overview of how clock and timing specifications have changed from PCI Express (PCIe) Generation 1, Gen 2, Gen 3, Gen 4 and Gen 5.

Presented by Ron Wade, system architect at IDT (acquired by Renesas). For more information, visit Renesas's PCIe Timing Solutions page.

A brief overview of the PCI Express common clock (CC) jitter model, and the transfer functions as they relate to the timing PLLs. This model applies to PCI Express (PCIe) Gen 2, Gen 3, Gen 4 and Gen 5. The equations would be slightly different for other PCIe architectures, such as SRIS, SRnS, or data clocked.

Presented by Ron Wade, system architect at IDT (acquired by Renesas). For more information about Renesas's PCIe timing solutions, visit the PCI Express (PCIe) Clocks page.