Features

- Supports AT&T TR62411 and Telcordia GR-1244-CORE Stratum 3, Stratum 4 Enhanced and Stratum 4 timing for DS1 interfaces

- Supports ITU-T G.813 Option 1 clocks for 2048 kbit/s interfaces

- Supports ITU-T G.812 Type IV clocks for 1544 kbit/s interface and 2048 kbit/s interfaces

- Supports ETSI ETS 300 011, TBR 4, TBR 12 and TBR 13 timing for E1 interface

- Selectable input reference signal: 8 kHz, 1.544 MHz or 2.048 MHz

- Accepts reference inputs from two independent sources

- Provides eight types of clock signals: C1.5o, C3o, C2o, C4o, C6o, C8o, C16o and C32o

- Provides six types of 8 kHz framing pulses: F0o, F8o, F16o, F32o, RSP and TSP

- Holdover frequency accuracy of 0.025 ppm

- Phase slope of 5 ns/125 ?s

- Attenuates wander from 2.1 Hz

- Fast Lock mode

- Provides Time Interval Error (TIE) correction

- MTIE of 600 ns

- JTAG boundary scan

- Holdover status indication

- Freerun status indication

- Normal status indication

- Lock status indication

- Input primary reference quality indication

- 3.3 V operation with 5 V tolerant I/O

- Package available: 56-pin SSOP (Green option available)

Description

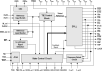

The 82V3002A is a WAN PLL with dual reference inputs. It contains a Digital Phase-Locked Loop (DPLL), which generates ST-BUS clocks and framing signals that are phase locked to a 2.048 MHz, 1.544 MHz or 8 kHz input reference. The 82V3002A provides eight types of clock signals (C1.5o, C3o, C6o, C2o, C4o, C8o, C16o, C32o) and six types of framing signals (F0o, F8o, F16o, F32o, RSP, TSP) for the multitrunk T1 and E1 primary rate transmission links. The 82V3002A is compliant with AT&T TR62411, Telcordia GR- 1244-CORE Stratum 3, Stratum 4 Enhanced and Stratum 4, ETSI ETS 300 011, ITU-T G.813 Option 1 for 2048 kbit/s interface, and ITU-T G.812 Type IV clocks for 1544 kbit/s interface and 2048 kbit/s interface. It meets the jitter/wander tolerance, jitter/wander transfer, intrinsic jitter/wander, frequency accuracy, capture range, phase change slope, holdover frequency accuracy and MTIE (Maximum Time Interval Error) requirements for these specifications. The 82V3002A can be used in synchronization and timing control for T1 and E1 systems, or used as ST-BUS clock and frame pulse sources. It can also be used in access switch, access routers, ATM edge switches, wireless base station controllers, or IADs (Integrated Access Devices), PBXs and line cards.

Applied Filters: