Features

- 2 - 0.7V current mode differential HCSL output pairs

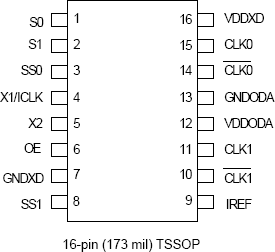

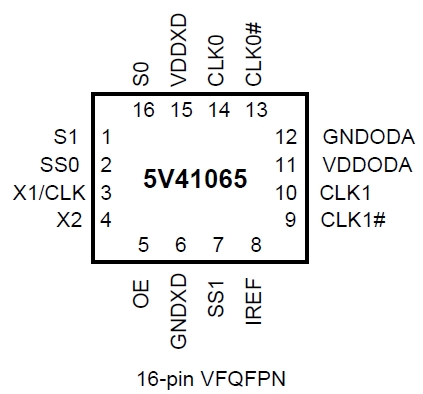

- 16-pin TSSOP and VFQFPN package; small board footprint

- Spread-spectrum capable; reduces EMI

- Outputs can be terminated to LVDS; can drive a wider variety of devices

- 25 MHz, 125 MHz and 200 MHz output frequencies; supports Ethernet applications

- OE control pin; greater system power management

- Spread% and frequency pin selection; no software required to configure device

- Industrial temperature range available; supports demanding embedded applications

- For PCIe Gen3 applications, see the 5V41235

- Cycle-to-cycle jitter < 100 ps

- Output-to-output skew < 50 ps

- PCIe Gen2 phase jitter < 3.0ps RMS

Description

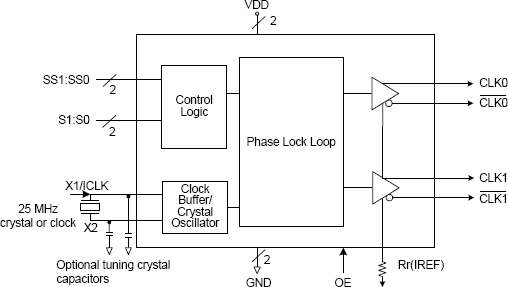

The 5V41065 is a PCIe Gen2 compliant spread spectrum capable clock generator. The device has 2 differential HCSL outputs and can be used in communication or embedded systems to substantially reduce electro-magnetic interference (EMI). The spread amount and output frequency are selectable via select pins. The 5V41065 can also supply 25 MHz, 125 MHz and 200 MHz outputs for applications such as Ethernet.

Parameters

| Attributes | Value |

|---|---|

| Temp. Range (°C) | -40 to 85°C, 0 to 70°C |

Applied Filters:

Filters

Software & Tools

Sample Code

Simulation Models

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

In this episode, Ron Wade from IDT (acquired by Renesas) explains PCIe common clocking and its impact on timing solutions. Learn about using a single clock source, fan-out buffers, and the considerations for spread spectrum and non-spread spectrum clocking in PCIe systems.

In this video, we explore PCIe with separate reference clocks and the effects of clock selection. Learn how separate reference clocks work and their impact on system performance and stability.

This video provides a high-level overview of Separate Reference Clock with Independent Spread (SRIS) architectures for PCI Express systems, additional performance requirements that this clocking architecture imposes on the reference clocks, and some system implications encountered trying to implement the architecture.