Features

- One 3.3Vdifferential LVPECL output pair and one LVCMOS/LVTTL single-ended reference clock output

- Selectable crystal oscillator interface or LVCMOS/LVTTL single-ended input

- Crystal and CLK range: 19.44MHz – 27MHz

- Able to generate GbE/10GbE/12GbE, Fibre Channel (1Gb/4Gb/10Gb), PCI-E and SATA from a 25MHz crystal

- VCO range: 1.12GHz – 1.275GHz

- Supports the following applications: SONET, Ethernet, Fibre Channel, Serial ATA, and HDTV

- RMS phase jitter @ 622.08MHz (12kHz - 20MHz): 0.9ps (typical), 3.3V

- Supply modes

VCC/VCCO

3.3V/3.3V

3.3V/2.5V

2.5V/2.5V - -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

Description

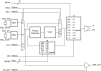

The 843001I-23 is a highly versatile, low phase noise LVPECL/LVCMOS synthesizer that can generate low jitter reference clocks for a variety of communication applications. The dual crystal interface allows the synthesizer to support up to three communication standards in a given application (i.e. SONET with a 19.44MHz crystal, 1Gb/10Gb Ethernet and Fibre Channel using a 25MHz crystal). The RMS phase jitter performance is typically less than 1ps, thus making the device acceptable for use in demanding applications such as OC48 SONET, GbE/10Gb Ethernet and SAN applications. The 843001I-23 is packaged in a small 24-pin TSSOP, E-Pad package.

Applied Filters: