Overview

Description

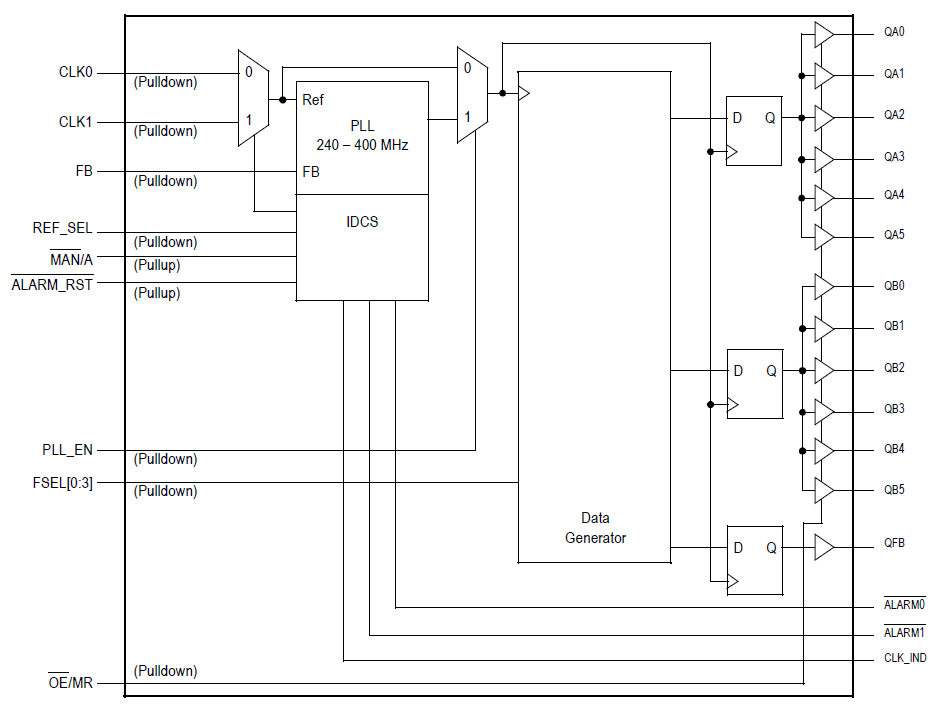

The MPC9893 is a 2.5 V and 3.3 V compatible, PLL based intelligent dynamic clock switch and generator specifically designed for redundant clock distribution systems. The device receives two LVCMOS clock signals and generates 12 phase aligned output clocks. The MPC9893 is able to detect a failing reference clock signal and to dynamically switch to a redundant clock signal. The switch from the failing clock to the redundant clock occurs without interruption of the output clock signal (output clock slews to alignment). The phase bump typically caused by a clock failure is eliminated. The device offers 12 low skew clock outputs organized into two output banks, each configurable to support the different clock frequencies. The extended temperature range of the MPC9893 supports telecommunication and networking requirements. The device employs a fully differential PLL design to minimize jitter.

Features

- 12-output LVCMOS PLL clock generator

- 2.5 V and 3.3 V compatible

- IDCS - on-chip intelligent dynamic clock switch

- Automatically detects clock failure

- Smooth output phase transition during clock failover switch

- 7.5 – 200 MHz output frequency range

- LVCMOS compatible inputs and outputs

- External feedback enables zero-delay configurations

- Supports networking, telecommunications and computer applications

- Output enable/disable and static test mode (PLL bypass)

- Low skew characteristics: maximum 50 ps output-to-output (within bank)

- 48-lead LQFP package

- 48-lead Pb-free package available

- Ambient operating temperature range of -40 to 85°C

Comparison

Applications

Design & Development

Support

Support Communities

Get quick technical support online from Renesas Engineering Community technical staff.