概要

説明

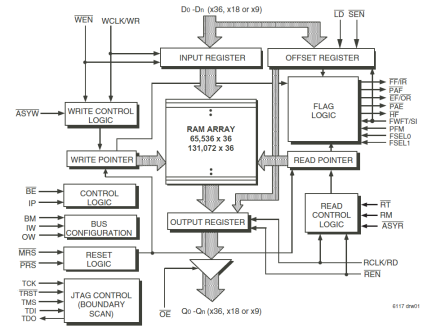

The 72V36100 64K x 36 SuperSync II FIFO memory with clocked read and write controls offers flexible Bus-Matching x36/x18/x9 data flow and Asynchronous/Synchronous translation on the read or write ports ; SuperSync II FIFO's are appropriate for network, video, telecommunications, data communications and other applications that need to buffer large amounts of data and match busses of unequal sizes.

特長

- Pin compatible to the SuperSync II 72V36x0 family

- Up to 166 MHz Operation of the Clocks

- User selectable Asynchronous read and/or write ports (PBGA Only)

- User selectable input and output port bus-sizing

- 5V input tolerant

- Auto power down minimizes standby power consumption

- Master Reset clears entire FIFO

- Partial Reset clears data, but retains programmable settings

- Easily expandable in depth and width

- JTAG port, provided for Boundary Scan function (PBGA Only)

- Independent Read and Write Clocks

- Available in 128-pin TQFP or 144-pin PBGA packages

- Industrial temperature range (–40C to +85C) is available

製品比較

アプリケーション

設計・開発

製品選択

適用されたフィルター