警告メッセージ

特長

- One differential LVDS output pair

- One differential clock input

- CLK, nCLK supports the following input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Input frequency range: 98MHz to 128MHz

- Output frequency range: 98MHz to 640MHz

- VCO range: 490MHz - 640MHz

- Cycle-to-cycle jitter: 50ps (maximum)

- Full 3.3V operating supply

- PCI Express® (2.5Gb/s) and Gen 2 (5 Gb/s) jitter compliant

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

説明

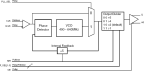

The 874001I-05 is a high performance Jitter Attenuator designed for use in PCI Express®™ systems. In some PCI Express® systems, such as those found in desktop PCs, the PCI Express® clocks are generated from a low bandwidth, high phase noise PLL frequency synthesizer. In these systems, a jitter attenuator may be required to attenuate high frequency random and deterministic jitter components from the PLL synthesizer and from the system board. The 874001I-05 has a bandwidth of 6MHz with <1dB peaking, easily meeting PCI Express® Gen2 PLL requirements. The 874001I-05 uses IDT's 3RD Generation FemtoClock® PLL technology to achieve the lowest possible phase noise. The device is packaged in a small 20-pin TSSOP package, making it ideal for use in space constrained applications such as PCI Express® add-in cards.

適用されたフィルター