特長

- Fully integrated PLL, no external loop filter required

- Differential 3.3 V LVPECL outputs

- Uses fundamental crystal or clock

- Crystal input frequency: 10 to 27MHz

- Clock input: 10 to 38MHz (multiply by 6)

- 0 to 31MHz (all other multiply settings)

- Output clocks up to 230 MHz at 3.3 V

- Low phase noise: -122 dBc/Hz at 10 kHz

- Low jitter - 15 ps one sigma typ.

- Powerdown mode lowers power consumption

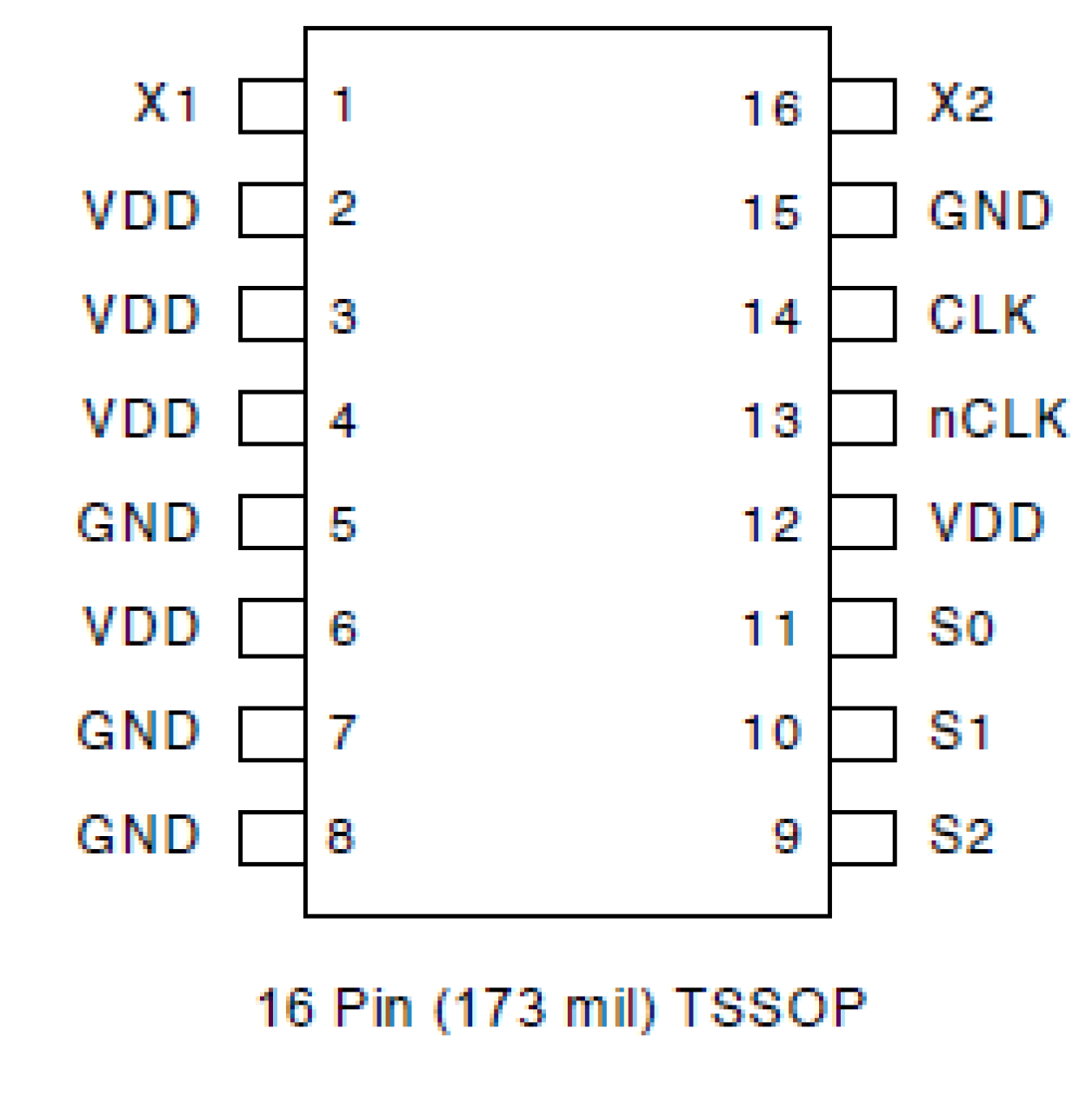

- Packaged in 16-pin TSSOP, Pb-free

- Advanced, low power, sub-micron CMOS process

- Operating voltage of 3.3 V

- Commercial temperature range available

説明

The ICS601-21 is a low-cost, low phase noise, high performance clock synthesizer for applications which require low phase noise and low jitter. It is Renesas’ lowest phase noise multiplier. Using Renesas’ patented analog and digital Phase Locked Loop (PLL) techniques, the chip accepts a crystal or clock input, and produces output clocks up to 230 MHz at 3.3 V. This product is intended for clock generation. It has low output jitter (variation in the output period), but input to output skew and jitter are not defined nor guaranteed.

適用されたフィルター

読込中