Overview

Description

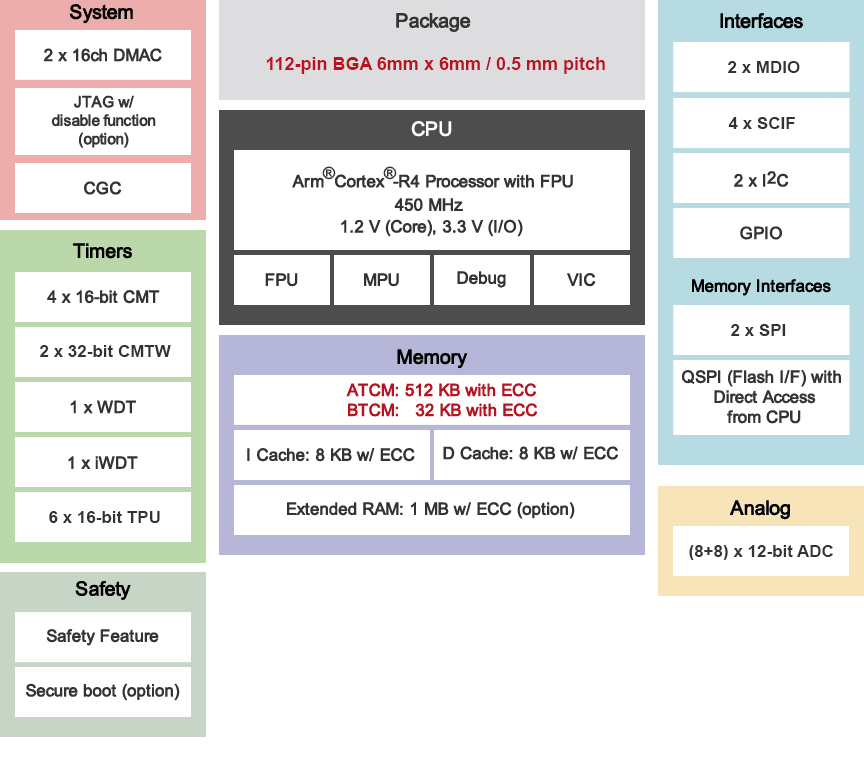

The RZ/T1-M group has the Arm® Cortex®-R4 Processor with FPU designed for real-time processing, capable of high-speed operation at up to 450 MHz. And by equipped with the MDIO interface, The RZ/T1-M group is ideal for applications such as optical modules. 6 x 6mm small package contributes to space saving.

Features

- CPU: Arm® Cortex®-R4 Processor with FPU, 450MHz

- Management data input / output interface(Slave/Master)

- Memory: Tightly Coupled Memory 544KB(with ECC), Extended SRAM 1MB(with ECC, option)

- Analog function: 12-bit A/D Converter Unit0 : 8ch,Unit1 : 8ch

- Package: 112-pin FBGA

- Voltage: Core 1.2V, I/O 3.3V

Comparison

Applications

Design & Development

Software & Tools

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Support

Support Communities

Resources

Support Communities

-

RZ/T1 MPUs endat info

Hello to all I saw in the manual RZ/T1 (example R7S910018CBG) that the Endat function is defined as "optional" .... I don't understand ... if I take a "sample" of this MPUs in the Renesas website this function is present or not. If I look for a "sample" MPUs ...

Nov 13, 2020 -

Thermal resistance of RZ/T1 Microprocessors

I can't find the thermal resistances for calculating junction temperature on the RZ/T1 processors. Can someone please help me with this information? or any alternate ways Thanks [locked by: Michael Quirk at 19:47 (GMT 0) on 24 Jul 2024]

Jul 24, 2024 -

RZ/T1 MCU -peripheral sharing issue

Hello. We plan to be new designers of the RZ/T1 MCU. we need to connect a FPGA to the MCU for deterministic serial data streams (target is 200Mbps) . Can we use the SPIBSC for that (shared with the S-Flash) ? can we use the RSPIa as quad SPI ...

Apr 20, 2020

FAQs

-

RZ/T1 : Memory barrier instructions

Cortex-R4 supports the following three memory barrier instructions. DMBMemory access instructions after DMB instruction are not executed until all memory accesses before DMB instruction are completed.However, instructions except memory access are executed.Execute DMB instruction when expecting that all memory accesses before DMB instruction will be completed. DSBInstructions ...

Mar 31, 2021 -

RZ/T1: Missing Parameters for the Loader in External Flash

The errors "Checksum error of the parameters for the loader" or "Error in a parameter for the loader" will occur and the CPU will go into a infinite loop during boot processing. Also, the error information is stored in the dedicated address of "0080 09C4h". For more details, refer to ...

Sep 27, 2017 -

RZ/T1 : MSL (Moisture Sensitivity levels)

MSL of RZ/T1 is 3. For details of MSL, refer to the following URL. https://www.renesas.com/us/en/support/technical-resources/packaging/packing/handling.html

Mar 5, 2021