Overview

Description

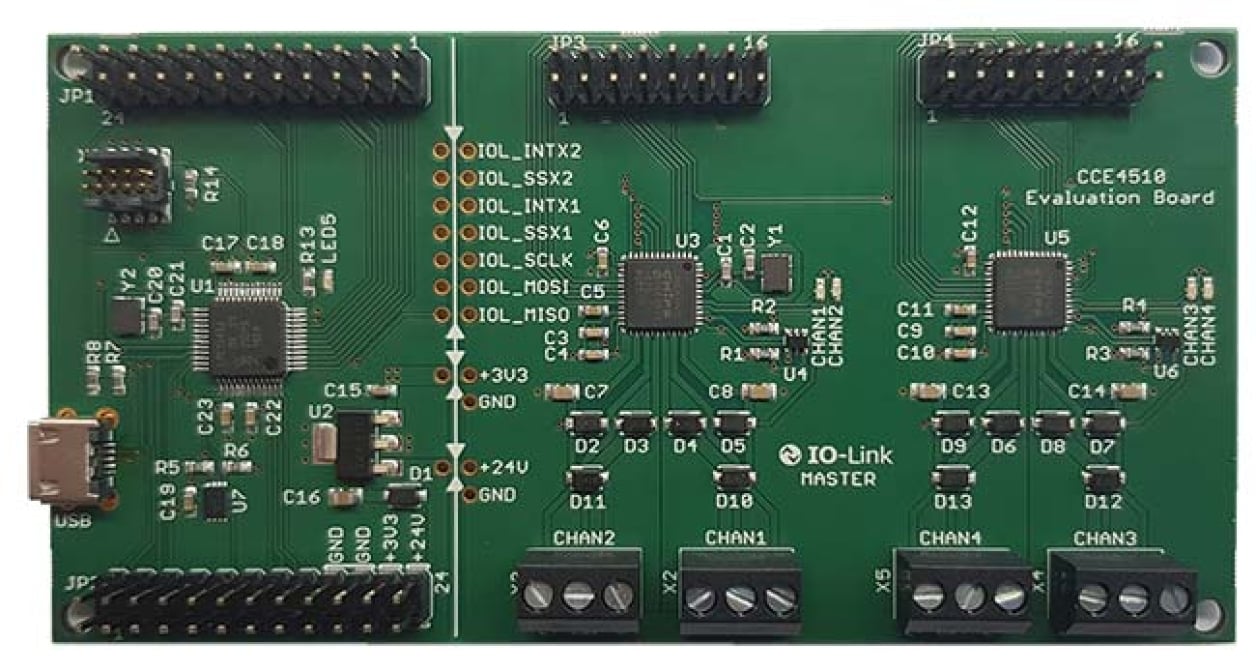

The CCE4510-EVAL-V2 evaluation board is designed to evaluate the CCE4510 IO-Link master IC with integrated frame handler.

The CCE4510 is a highly integrated IO-Link master PHY IC providing two IO-Link compliant channels with 1A peak driving current. The built-in IO-Link hardware frame handler significantly improves application performance by automating most of the lower layer communication tasks. By reducing the microcontroller load, CCE4510 frees up valuable processing bandwidth enabling developers to add greater value by running additional processor-intensive tasks without the need for higher performance microcontrollers.

Features

- Arm® Cortex®-M3 microcontroller

- On-board 3.3V LDO

- 16kB EEPROM

- Programmable via USB or serial wire debug (SWD)

- Status LED indicator

- External NMOS gate drivers

- 24V supply voltage

- Two CCE4510 IO-Link master transceiver ICs

- Four IO-Link channels

- Four status LED indicators for IO-Link channels

- Additional on-board protection circuitry

- All pins accessible via pin-headers

- For microcontroller and IO-Link master ICs

- Independent use of sections

Applications

Support

Support Communities

Get quick technical support online from Renesas Engineering Community technical staff.

Knowledge Base

Browse our knowledge base for helpful articles, FAQs, and other useful resources.