Overview

Description

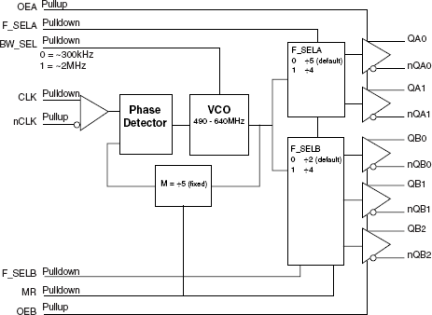

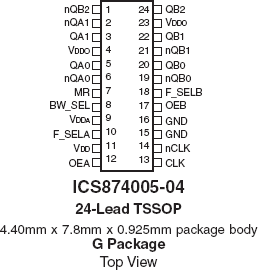

The 874005-04 is a high performance Differential- to-LVDS Jitter Attenuator designed for use in PCI Express® systems. In some PCI Express® systems, such as those found in desktop PCs, the PCI Express® clocks are generated from a low bandwidth, high phase noise PLL frequency synthesizer. In these systems, a jitter attenuator may be required to attenuate high frequency random and deterministic jitter components from the PLL synthesizer and from the system board. The 874005-04 has 2 PLL bandwidth modes: 300kHz and 2MHz. The 300kHz mode will provide maximum jitter attenuation, but higher PLL tracking skew and spread spectrum modulation from the motherboard synthesizer may be attenuated. The 2MHz bandwidth provides the best tracking skew and will pass most spread profiles. The 874005-04 supports Serdes reference clock frequencies of 100MHz, 125MHz and 250MHz. The 874005-04 uses IDT's 3rd Generation FemtoClockTM PLL technology to achieve the lowest possible phase noise. The device is packaged in a 24 Lead TSSOP package, making it ideal for use in space constrained applications such as PCI Express® add-in cards.

Features

- Five differential LVDS output pairs

- One differential clock input

- Supports 100MHz, 125MHz, and 250MHz Serdes reference clocks

- CLK and nCLK supports the following input types: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Output frequency range: 98MHz - 320MHz

- Input frequency range: 98MHz - 128MHz

- PCI Express® (2.5 Gb/S) and Gen 2 (5 Gb/s) jitter compliant

- RMS phase jitter @ 100MHz (1.875MHz - 20MHz): 0.88ps (typical)

- VCO range: 490MHz - 640MHz

- Cycle-to-cycle jitter: 35ps (maximum) QA = QB = ÷4

- 3.3V operating supply

- Two bandwidth modes allow the system designer to make jitter attenuation/tracking skew design trade-offs

- 0°C to 70°C ambient operating temperature

- Available in lead-free (RoHS 6) package

Comparison

Applications

Design & Development

Product Options

Applied Filters:

Videos & Training

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

Watch the Video Series Below