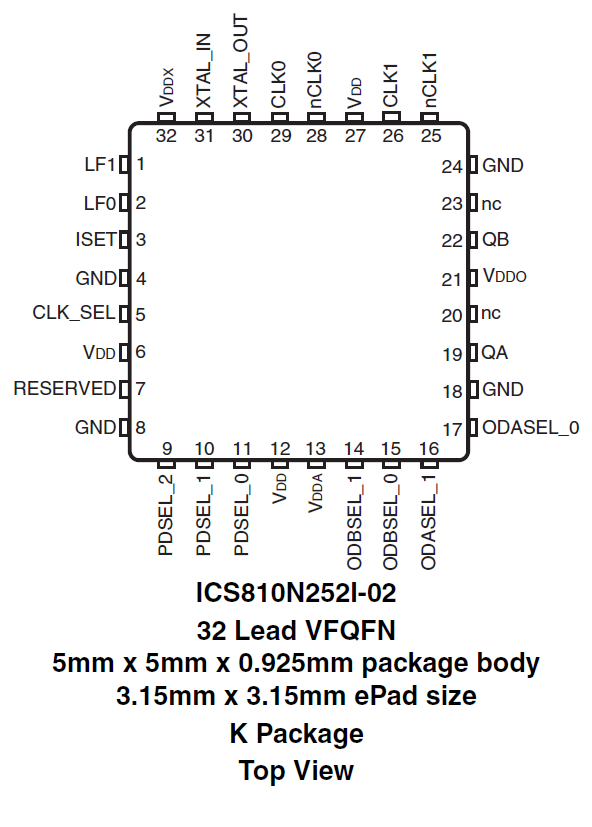

Package Information

| Lead Count (#) | 32 |

| Pkg. Code | NLG32 |

| Pitch (mm) | 0.5 |

| Pkg. Type | VFQFPN |

| Pkg. Dimensions (mm) | 5.0 x 5.0 x 0.9 |

Environmental & Export Classifications

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

Product Attributes

| Lead Count (#) | 32 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to +85°C |

| Abs. Pull Range Min. (± PPM) | 50 |

| Advanced Features | VCXO-based APLL |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 0.008 - 155.52 |

| Input Type | HCSL, LVDS, LVPECL, LVHSTL |

| Inputs (#) | 2 |

| Length (mm) | 5 |

| Loop Bandwidth Range (Hz) | 15 - 60 |

| MOQ | 2500 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 25 - 25, 125 - 125, 156.25 - 156.25, 312.5 - 312.5 |

| Output Skew (ps) | 80 |

| Output Type | LVCMOS, LVTTL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 2 |

| Package Area (mm²) | 25.0 |

| Phase Jitter Typ RMS (ps) | 0.670 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 5.0 x 5.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 0.9 |

| Width (mm) | 5 |

| Xtal Freq (KHz) | 27 - 27 |

Resources for 810N252I-02

Description

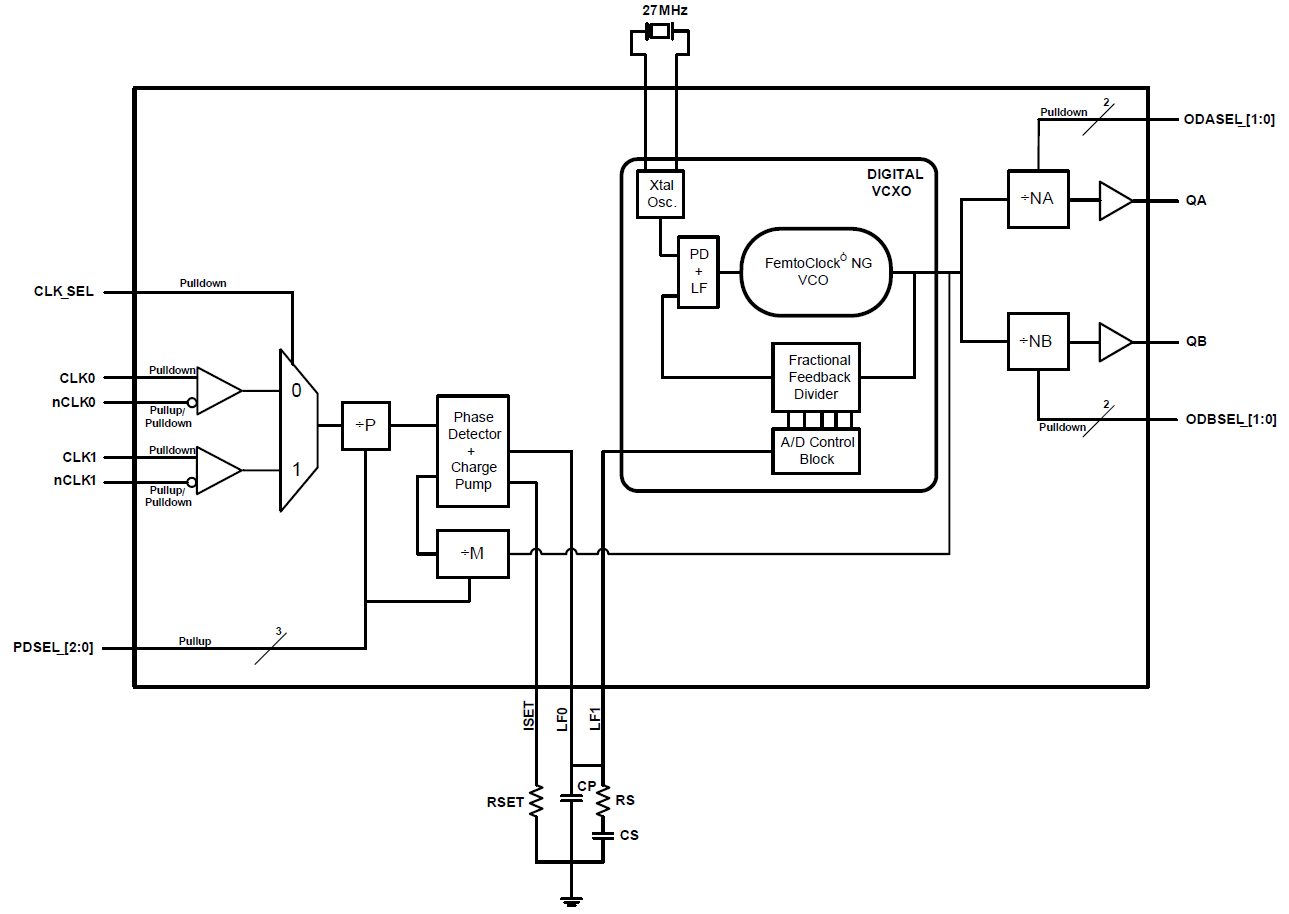

The 810N252I-02 device uses Renesas' fourth generation FemtoClock® NG technology for optimal high clock frequency and low phase noise performance, combined with low power consumption and high power supply noise rejection. The 810N252I-02 is a PLL-based synchronous multiplier optimized for PDH or SONET to Ethernet clock jitter attenuation and frequency translation.

The 810N252I-02 contains two internal frequency multiplication stages that are cascaded in series. The first stage is a jitter attenuator, capable of jitter attenuation down to 10Hz using the external loop filter. The second stage is a FemtoClock NG frequency multiplier that provides the low jitter, high-frequency Ethernet output clock that easily meets Gigabit and 10 Gigabit Ethernet jitter requirements. Pre-divider and output divider multiplication ratios are selected using device selection control pins. The multiplication ratios are optimized to support most common clock rates used in PDH, SONET, and Ethernet applications. The device requires the use of an external, inexpensive fundamental mode 27MHz crystal. It is packaged in a space-saving 32-VFQFN package and supports the industrial temperature range.