Overview

Description

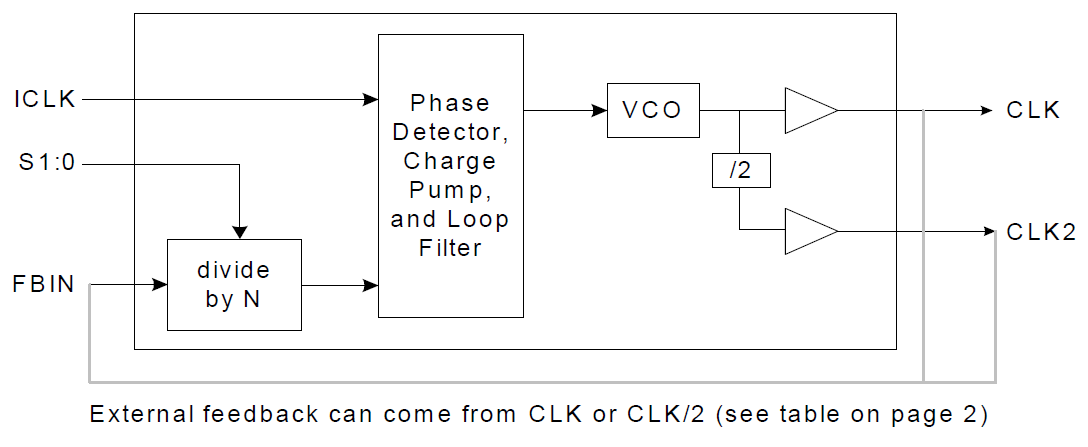

The IDT570 is a high-performance Zero Delay Buffer (ZDB) which integrates IDT's proprietary analog/digital Phase Locked Loop (PLL) techniques. The A version is recommended for 5 V designs and the B version for 3.3 V designs. The chip is part of IDT's ClockBlocks™ family, and was designed as a performance upgrade to meet today's higher speed and lower voltage requirements. The zero delay feature means that the rising edge of the input clock aligns with the rising edges of both output clocks, giving the appearance of no delay through the device. There are two outputs on the chip, one being a low-skew divide by two of the other output. The device incorporates an all-chip power down/tri-state mode that stops the internal PLL and puts both outputs into a high impedance state. The IDT570 is ideal for synchronizing outputs in a large variety of systems, from personal computers to data communications to graphIDT/video. By allowing off-chip feedback paths, the device can eliminate the delay through other devices.

Features

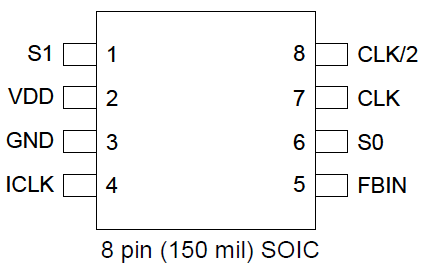

- Packaged in 8-pin SOIC

- Available in Pb (lead) free package

- Pin-for-pin replacement and upgrade to IDT570M

- Functional equivalent to AV9170 (not a pin-for-pin replacement).

- Low input to output skew of 300 ps max (>60 MHz outputs)

- Low skew (100ps) outputs. One is ÷ 2 of other

- Ability to choose between 14 different multipliers from 0.5X to 32X

- Output clock frequency up to 168 MHz at 3.3 V

- Can recover degraded input clock duty cycle

- Output clock duty cycle of 45/55

- Power-down and Tri-State mode

- Passes spread spectrum clock modulation

- Full CMOS clock swings with 25 mA drive capability at TLL levels

- Advanced, low power CMOS process

- IDT570B has an operating voltage of 3.3 V

- IDT570A has an operating voltage of 5.0V

- Industrial temperature version available

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Support

Support Communities

Support Communities

-

Info about H8/570 ISP

I'm looking for a specific document regarding the H8/570 16-bit MCU. The document is called "ISP Hardware Manual", which should explain how the ISP (Intelligent Sub Processor) is supposed to work. Is it available anywhere?

Jun 25, 2024 -

rz/a1 info

Hi all, I'm evaluating rz/a1 for our linux based audio project, and I need some info to start. 1)The package we select is 256pin bga, do you know if the BSP(with XIP) for RSK+RZA1H still works? 2)To reduce size, can I use only ...

Sep 28, 2015 -

RX63N - RSPI in slave mode

I want a communication with SPI in Slave mode. I get the first byte, but at the second I get no interrupt. I see with the debugger, that the request flag is set and the interrupt is enable. Is there an error (e.g. Overflow, Buffer empty..)? The Transmit interrupt ...

Sep 28, 2015