Overview

Description

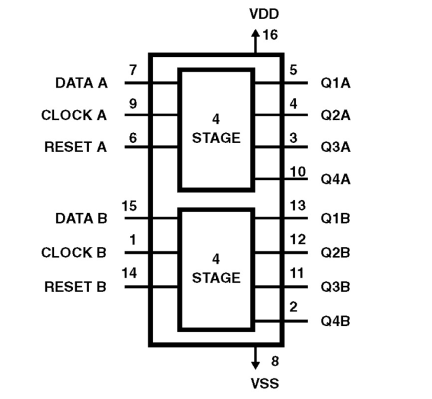

CD4015BMS consists of two identical, independent, 4-stage serial-input/parallel output registers. Each register has independent CLOCK and RESET inputs as well as a single serial DATA input. Q outputs are available from each of the four stages on both registers. All register stages are D type, master-slave flip-flops. The logic level present at the DATA input is transferred into the first register stage and shifted over one stage at each positive-going clock transition. Resetting of all stages is accomplished by a high level on the reset line. Register expansion to 8 stages using one CD4015BMS package, or to more than 8 stages using additional CD4015BMS's is possible. The CD4015BMS is supplied in these 16 lead outline packages: Braze Seal DIP H4X Frit Seal DIP H1F Ceramic Flatpack H6W

Features

- High voltage type (20V rating)

- Medium speed operation 12MHz (typ.) clock rate at VDD - VSS = 10V

- Fully static operation

- 8 master-slave flip-flops plus input and output buffering

- 100% tested for quiescent current at 20V

- 5V, 10V and 15V parametric ratings

- Standardized symmetrical output characteristics

- Maximum input current of 1µA at 18V over full package - temperature range; 100nA at 18V and 25 °C

- Noise margin (full package - temperature range) = 1V at VDD = 5V, 2V at VDD = 10V, 2.5V at VDD = 15V

- Meets all requirements of JEDEC tentative standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

Comparison

Applications

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 415 KB | |

| Brochure | PDF 467 KB | |

| Price Increase Notice | PDF 360 KB | |

| Other | ||

| Product Advisory | PDF 499 KB | |

| Product Change Notice | PDF 230 KB | |

6 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters: