Number of H8S/H8SX Multiplication Instruction Execution Cycles

| Operation | Number of Execution Cycles | |

|---|---|---|

| H8S | H8SX | |

| Unsigned Multiplication 16 bits x 16 bits — 32 bits 8 bits x 8 bits — 16 bits | 3 - 4 | 1 |

| Signed Multiplication 16 bits x 16 bits — 32 bits 8 bits x 8 bits — 16 bits | 4 - 5 | 2 |

| Unsigned Multiplication Rd x Rs — Rd (lower 32 bits/lower 16 bits) | — | 2 - 5 |

| Signed Multiplication Rd x Rs — Rd (lower 32 bits/lower 16 bits) | — | 2 - 5 |

| Unsigned Multiplication Rd x Rs — Rd (upper 32 bits) | — | 6 |

| Signed Multiplication Rd x Rs — Rd (upper 32 bits) | — | 6 |

Number of H8S/H8SX Division Instruction Execution Cycles

| Operation | Number of Execution Cycles | |

|---|---|---|

| H8S | H8SX | |

| Unsigned Division 16 bits/8 bits — 8 bits with a remainder of 8 bits 32 bits/16 bits — 16 bits with a remainder of 16 bits | 12 - 20 | 10 - 18 |

| Signed Division 16 bits/8 bits — 8 bits with a remainder of 8 bits 32 bits/16 bits — 16 bits with a remainder of 16 bits | 14 - 21 | 12 - 20 |

| Unsigned Division Rd/Rs — Rd (quotient of 16 bits/ a quotient of 32 bits) | — | 10 - 18 |

| Signed Division Rd/Rs — Rd (quotient of 16 bits/a quotient of 32 bits) | — | 11 - 19 |

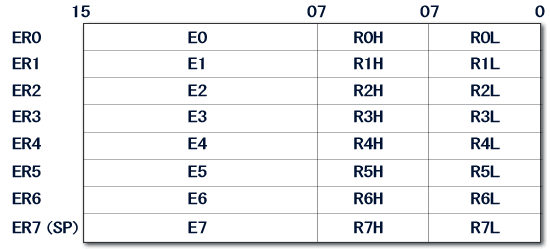

Configuration of General Registers

How to Use General Registers

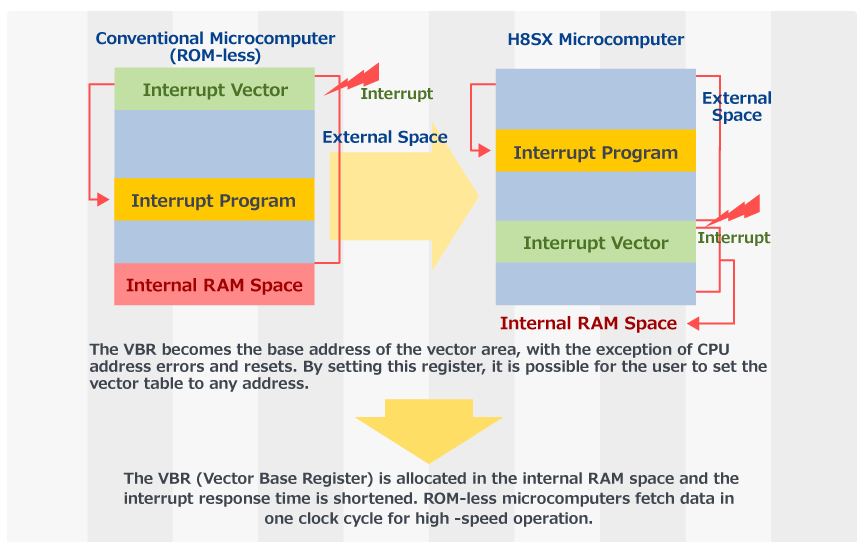

H8SX Vector Base Register (VBR) Usage Example

H8SX Short Address Base Register (SBR) Usage Example

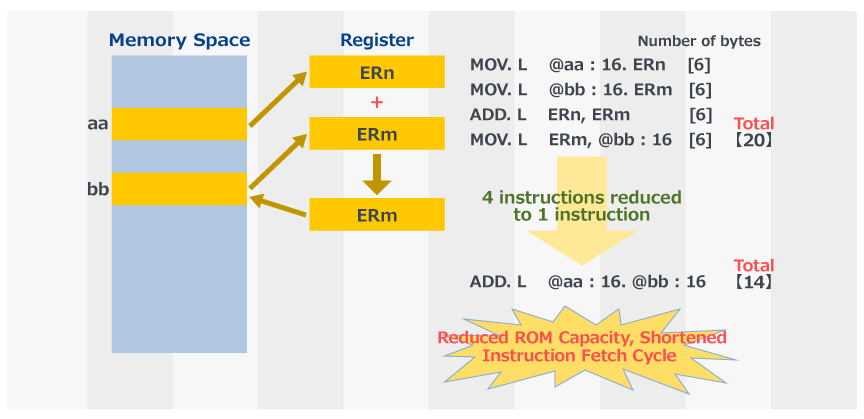

1. Support for Operations Using Memory

Additional instructions = Basic operations (add-subtract/logic) × basic addressing

Example: Adjustment of Long Word Data in Memory

2. Improved Addressing Mode - For Arrays

Example: Data from Address d to Address x is Written to a Register (Word Data)

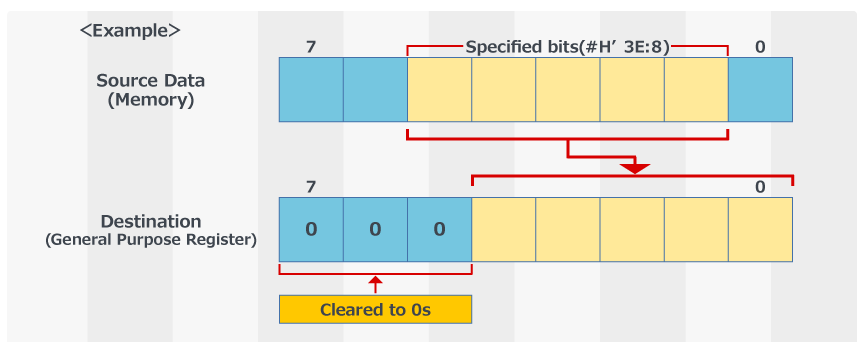

Bit Field Transfer (1)

*BFLD (Bit Field LoaD)

Example: The specified field where source operand is assigned and transferred to the 8-bit register Rd from the lower bits. The bit field is specified by the bit which is set to 1 in the 8-bit immediate data.

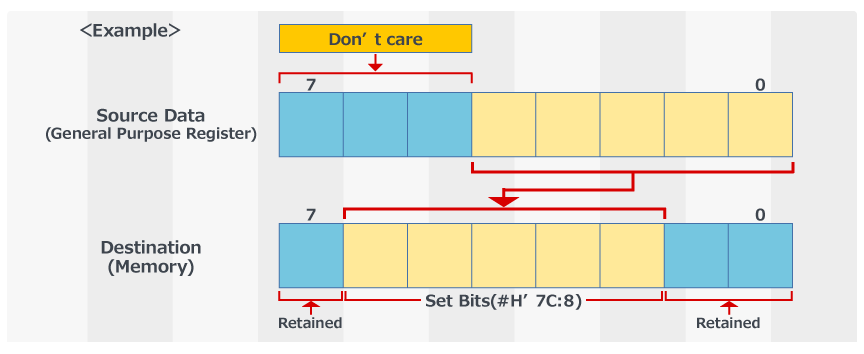

Bit Field Transfer (2)

>BFST (Bit Field STore)

Contents of 8-bit register Rs are transferred to the field where the destination operand is specified. The bit field is specified by the bit which is set to 1 in the 8-bit immediate data.

Support

Support Communities

Get quick technical support online from Renesas Engineering Community technical staff.

Knowledge Base

Browse our knowledge base for helpful articles, FAQs, and other useful resources.