Features

- DIF output cycle-to-cycle jitter < 50ps

- DIF output-to-output skew < 150 ps

- PCIe Gen2 compliant phase noise

- QPI 133MHz compliant phase noise

- Supports output clock frequencies up to 400 MHz

- 4 Selectable SMBus addresses

- SMBus address is independent of PLL operating mode

- Dedicated CKPWRGD/PD# and VDDA pins ease board design

- Available in industrial temperature range (-40°C to +85°C)

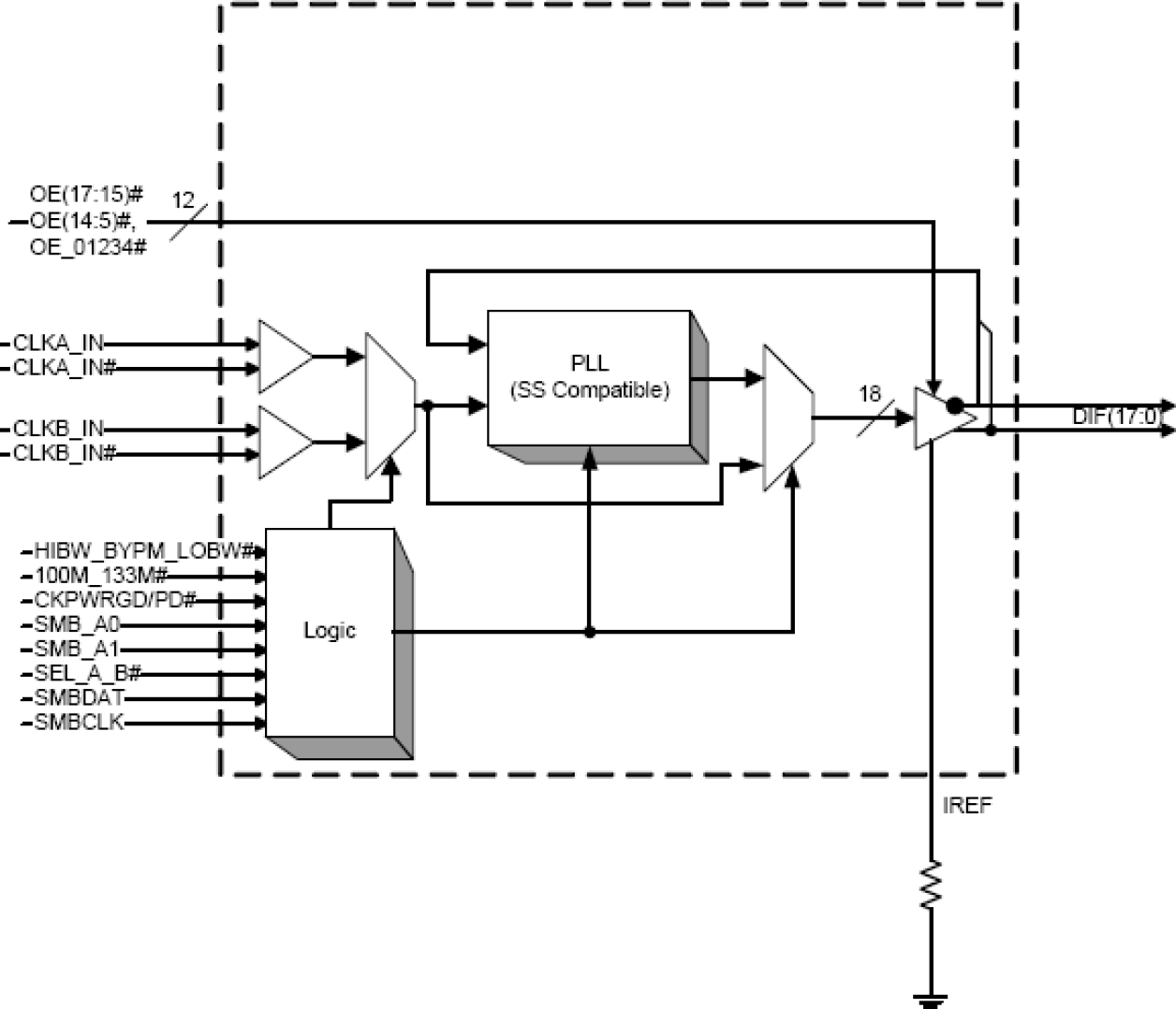

Description

The 9EX21801 provides 18 output clocks for PCIe Gen2 (100MHz) or QPI (133MHz) applications. The 9EX21801 has 4 selectable SMBus addresses, and dedicated CKPWRGD/PD# and VDDA pins for easy board design. A differential CPU clock from a CK410B+ main clock generator, such as the 932S421, drives the 9EX21801. In fanout mode, the 9EX21801 provides outputs up to 400MHz.

Applied Filters: