Features

- SMU allows any IEEE 1588 software, running on an external processor, to control the generation of electrical clocks, and to access and control physical layer synchronization

- Supports Telecom Boundary Clock (T-BC) and Telecom Time Slave Clock (T-TSC) applications per G.8273.2 with physical layer frequency support to the DCOs

- Physical layer clocks comply with ITU-T G.8262 for Synchronous Ethernet Equipment Clock (EEC), and G.813 for Synchronous Equipment Clock (SEC), and Telcordia GR-253-CORE for Stratum 3 and SONET Minimum Clock (SMC)

- System-wide precise 1PPS (Pulse Per Second) edge alignment is supported with programmable input-to-input, input-to-output and output-to-output phase delays: sub-ns resolution

- 24 hour time holdover is supported by DCOs with fine frequency resolution (1.7e-16);Generates clocks for: Ethernet, SONET/SDH and PDH interfaces: jitter generation <1 ps RMS (12 kHz to 20 MHz)

- IEEE 1588 grand master applications are supported by locking to 1 PPS (Pulse Per Second) references from GPS or other GNSS sources

- Eases local oscillator sourcing by supporting any of eight common TCXO/OCXO frequencies for the System Clock: 10 MHz, 12.8 MHz, 13 MHz, 19.44 MHz, 20 MHz, 24.576 MHz, 25 MHz or 30.72 MHz

- Automatically loads configuration from an external EPROM after reset without processor intervention

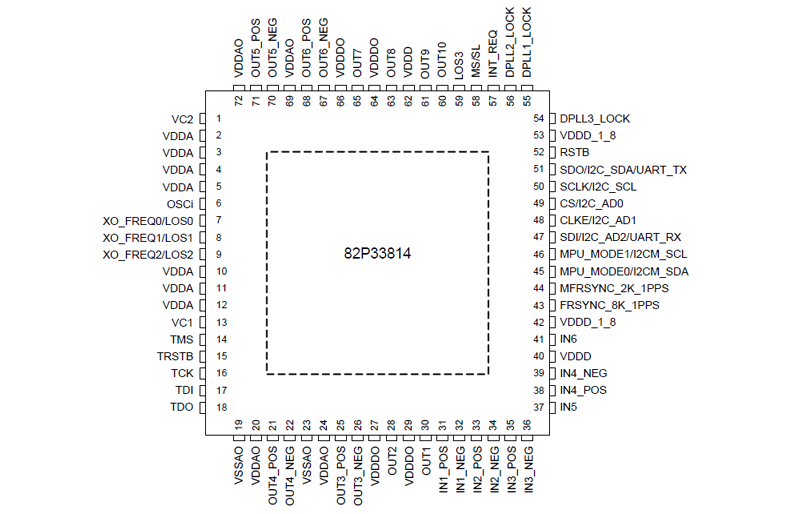

- 72 pin QFN package

Description

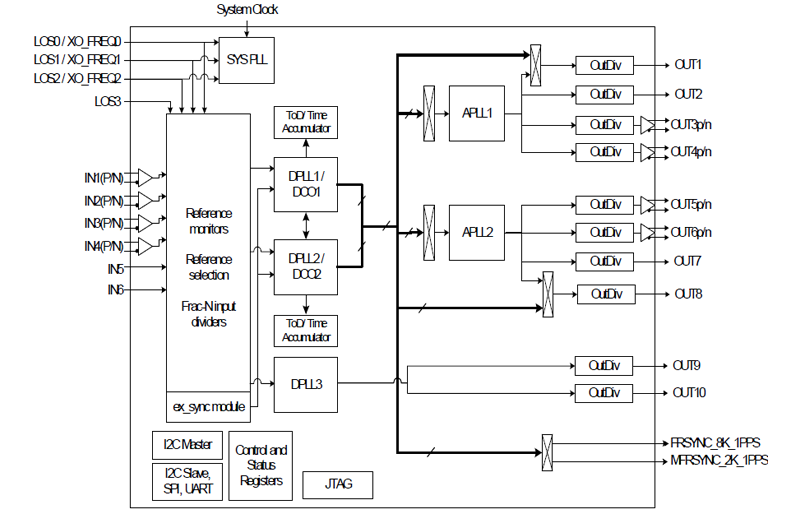

The 82P33814 Synchronization Management Unit (SMU) provides tools to manage timing references, clock sources and timing paths for IEEE 1588 and Synchronous Ethernet (SyncE) based clocks. The device supports up to three independent timing paths that control: IEEE 1588 clock synthesis; SyncE clock generation; and general purpose frequency translation.The device supports physical layer timing with Digital PLLs (DPLLs) and it supports packet based timing with Digitally Controlled Oscillators (DCOs). Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs low-jitter clocks that can directly synchronize Ethernet interfaces; as well as SONET/SDH and PDH interfaces and IEEE 1588 Time Stamp Units (TSUs).

Parameters

| Attributes | Value |

|---|---|

| Temp. Range (°C) | -40 to 85°C |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 10.0 x 10.0 x 1.0 | 72 | 0.5 |

Applied Filters: