Overview

Description

The ADC1213D is a dual channel 12-bit Analog-to-Digital Converter (ADC) optimized for high dynamic performances and low power at sample rates up to 65 Msps. Pipelined architecture and output error correction ensure the ADC1213D is accurate enough to guarantee zero missing codes over the entire operating range. Supplied from a 3.3 V source for analog and a 1.8 V source for the output driver, it can output data in serial mode, because of the two lanes of differential outputs, which are compliant with the JESD204A standard.

Features

- 2 configurable serial outputs

- Compliant with JESD204A serial transmission standard

- Dual channel 12-bit pipelined ADC core

- High IF capability

- Input bandwidth, 600 MHz

- Power-down and Sleep modes

- Sample rate up to 65 Msps

- SPI interface

Comparison

Applications

Documentation

Featured Documentation

Log in required to subscribe

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 589 KB | |

| End Of Life Notice | PDF 994 KB | |

2 items

|

||

Design & Development

Boards & Kits

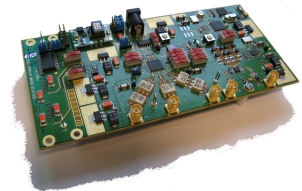

ADC1213D065W1

Obsolete

ADC1213D065W1 Demo board With FPGA

IDT's ADC demoboard is suitable for dynamic performance evaluations from low to high IF configuration. The FPGA eases the evaluation and analysis of the ADC dynamic and enables use of the full JESD204A feature set.

ADC1213D065WO

Obsolete

ADC1213D065WO demo board; compliant with Lattice, Altera, Xilinx FPGA boards through specific connectors

Our ADC demonstration board is suitable for dynamic performances evaluation from low to high IF configuration. A FPGA mother board (Xilinx, Altera, and Lattice) could be connected to ease the evaluation and analysis of the ADC dynamic and enable usage of the JESD204A full features sets

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters: