概要

説明

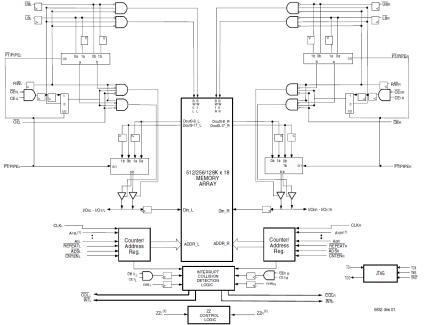

The 70T3319 is a high-speed 256K x 18 bit synchronous Dual-Port RAM that has been optimized for applications having unidirectional or bidirectional data flow in bursts. An automatic power down feature, controlled by CE0 and CE1, permits the on-chip circuitry of each port to enter a very low standby power mode. The 70T3319 can support an operating voltage of either 3.3V or 2.5V on one or both ports, controllable by the OPT pins. The power supply for the core of the device (VDD) is at 2.5V.

特長

- Dual-Port allows simultaneous access of the same memory location

- Selectable Pipelined or Flow-Through output mode

- Counter enable and repeat features

- Dual chip enables allow for depth expansion without additional logic

- Interrupt and Collision Detection Flags

- Full synchronous operation on both ports

- Separate byte controls for multiplexed bus and bus matching compatibility

- Dual Cycle Deselect (DCD) for Pipelined Output Mode

- 2.5V (±100mV) power supply for core

- LVTTL compatible, selectable 3.3V (±150mV) or 2.5V (±100mV) power supply for I/Os and control signals on each port

- Available in a 256-pin BGA and 208-pin fpBGA packages

- Includes JTAG functionality

- Industrial temperature range (-40C to +85C) is available

製品比較

アプリケーション

設計・開発

製品選択

適用されたフィルター