概要

説明

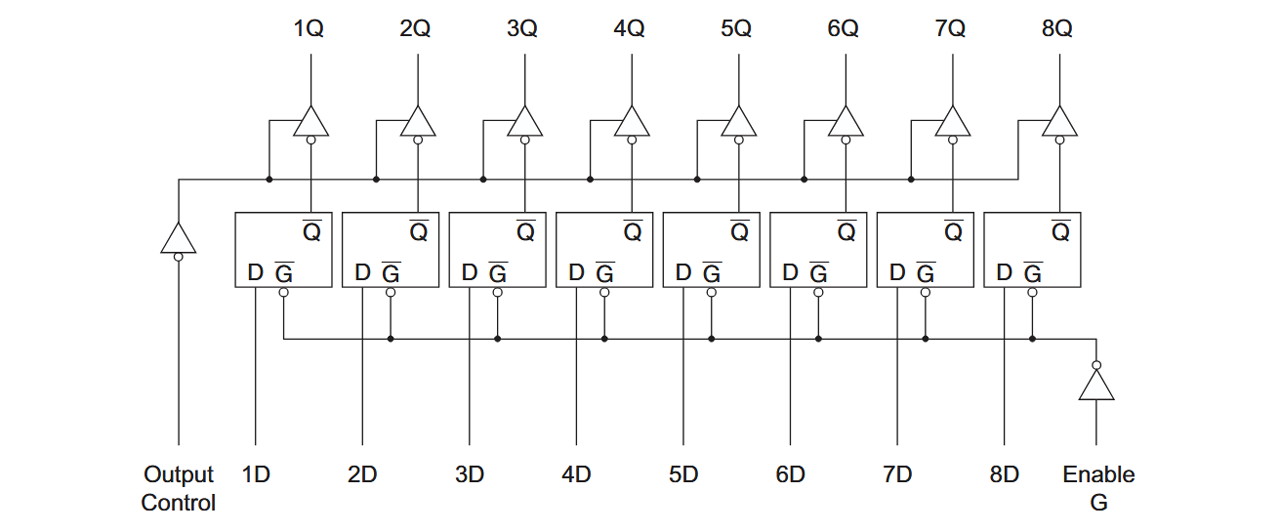

The HD74LS373, 8-bit register features totem-pole three-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. The high-impedance third state and increased high-logic-level drive provide this register with the capacity of being connected directly to and driving the bus lines in a bus-organized system without the need for interface or pull-up components. They are particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers. The eight latches are transparent D-type latches, meaning that while the enable (G) is high, the Q outputs will follow the data (D) inputs. When the enable is taken low, the output will be latched at the level of the data that was set up.

製品比較

アプリケーション

ドキュメント

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 313 KB English | |

| 製品変更通知 | PDF 4.87 MB English | |

| 製品変更通知 | PDF 3.82 MB English | |

| 製品変更通知 | PDF 1.91 MB English | |

| カタログ | PDF 5.23 MB | |

| カタログ | PDF 1.32 MB | |

|

6件

|

||

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。