パッケージ情報

| CADモデル: | View CAD Model |

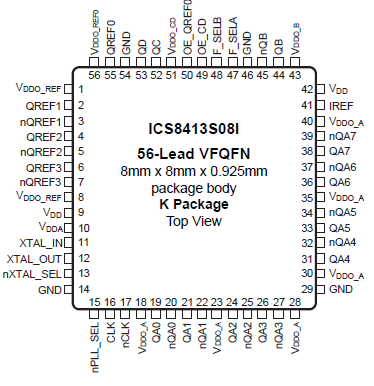

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG48 |

| Lead Count (#): | 48 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 0.9 |

| Pitch (mm): | 0.5 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Lead Count (#) | 48 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 260 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 25 - 25 |

| Input Type | LVCMOS, Crystal |

| Inputs (#) | 2 |

| Length (mm) | 7 |

| MOQ | 260 |

| Output Banks (#) | 5 |

| Output Freq Range (MHz) | 25 - 25, 312.5 - 312.5, 50 - 50, 100 - 100, 125 - 125, 156.25 - 156.25 |

| Output Signaling | HCSL, LVPECL, LVCMOS, LVDS |

| Output Type | HCSL, LVPECL, LVCMOS, LVDS |

| Output Voltage (V) | 3.3V, 2.5V |

| Outputs (#) | 10 |

| Package Area (mm²) | 49 |

| Phase Jitter Max RMS (ps) | 1.3 |

| Phase Jitter Typ RMS (ps) | 0.64 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Prog. Clock | No |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | No |

| Thickness (mm) | 0.9 |

| Width (mm) | 7 |

| Xtal Freq (KHz) | 25 - 25 |

| Xtal Inputs (#) | 1 |

| 掲載 | No |

8413S06I に関するリソース

説明

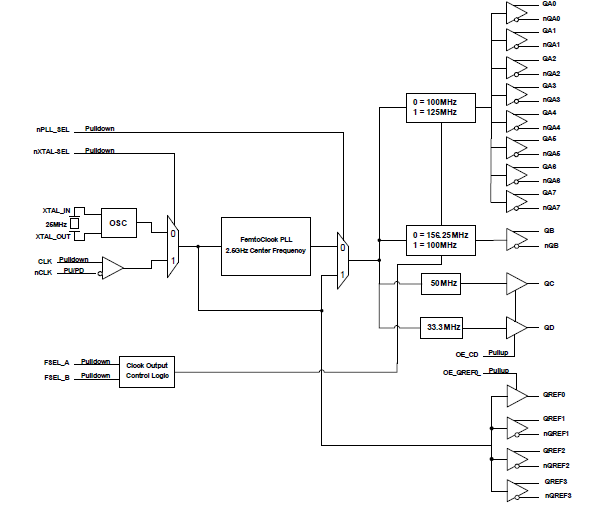

The 8413S06 is a PLL-based clock generator specifically designed for Cavium Networks Octeon II processors. This high-performance device is optimized to generate the processor core reference clock, sRIO, XAUI, SGMII SerDes reference clocks and the clocks for both the Gigabit Ethernet MAC and PHY. The clock generator offers ultra-low jitter, low-skew clock outputs, and edge rates that easily meet the input requirements for the CN63XX and CN68XX series of processors. The output frequencies are generated from a 25MHz external input source or an external 25MHz parallel resonant crystal.The industrial temperature range of the 8413S06 supports telecommunication, networking, and storage requirements.