Warning message

Please log in or register to access this secure document.

Features

- Packaged in 20-pin TSSOP

- RoHS 5 (green) or RoHS 6 (green and lead free) complaint package

- Supports PCI-Express applications

- Four differential spread spectrum clock outputs

- Spread spectrum for EMI reduction

- Uses external 25 MHz clock or crystal input

- Power down pin turns off chip

- OE control tri-states outputs

- Spread and frequency selection via external pins

- Spread Bypass option available

- Industrial temperature range available

- For PCIe Gen2 applications, see the 5V41066

- For PCIe Gen3 applications, see the 5V41236

Description

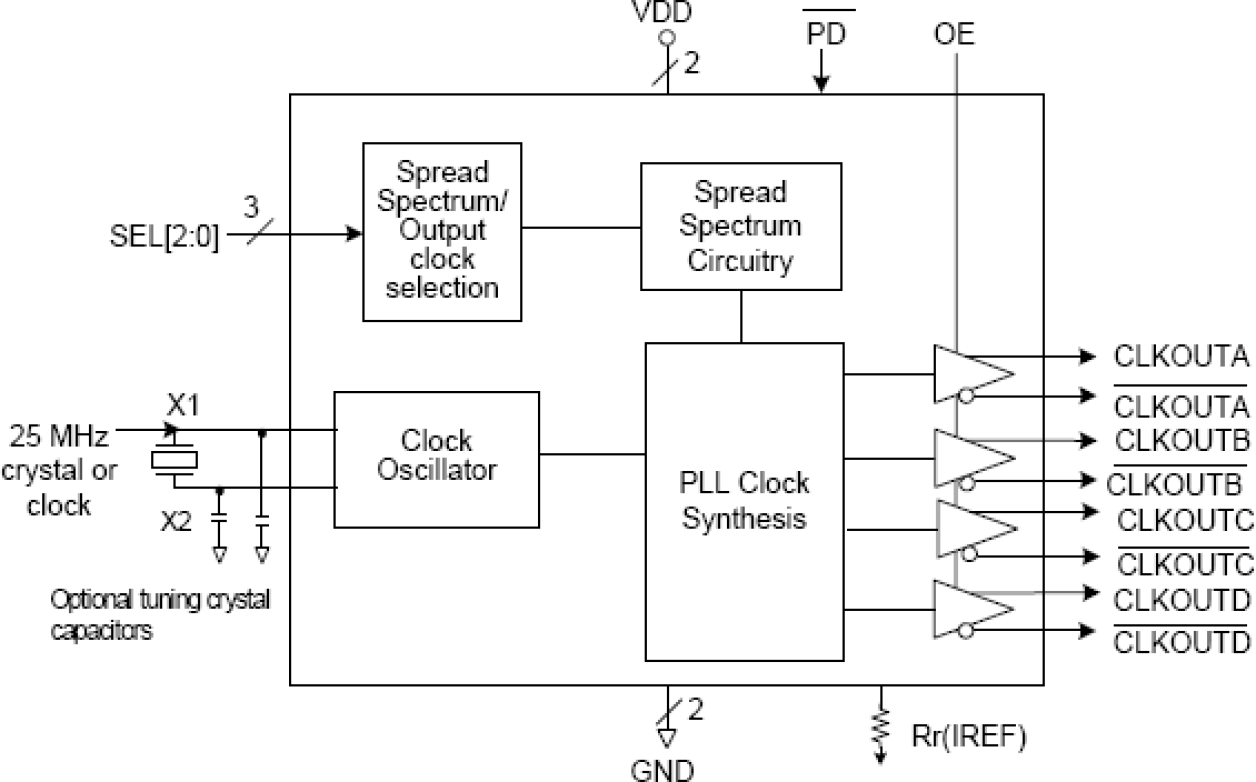

The 557-05A is a spread-spectrum clock generator that supports PCI-Express requirements. It is used in PC or embedded systems to substantially reduce electro-magnetic interference (EMI). The device provides four differential HCSL or LVDS high-frequency outputs with spread spectrum capability. The output frequency and spread type are selectable using external pins.

Parameters

| Attributes | Value |

|---|---|

| Diff. Outputs | 4 |

| Diff. Output Signaling | HCSL |

| Output Freq Range (MHz) | 100 - 100, 200 - 200 |

| Power Consumption Typ (mW) | 396 |

| Supply Voltage (V) | 3.3 - 3.3 |

| Output Type | HCSL |

| Xtal Freq (MHz) | 25 - 25 |

| Diff. Termination Resistors | 16 |

| Package Area (mm²) | 28.6 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 25 - 25 |

| Input Type | Crystal, LVCMOS |

| Output Banks (#) | 1 |

| Core Voltage (V) | 3.3 |

| Output Voltage (V) | 3.3 |

| Product Category | PCI Express Clocks |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TSSOP | 6.5 x 4.4 x 1.0 | 20 | 0.65 |

Applied Filters: