Package Information

| Lead Count (#) | 128 |

| Pkg. Code | PK128 |

| Pitch (mm) | 0.5 |

| Pkg. Type | TQFP |

| Pkg. Dimensions (mm) | 20.0 x 14.0 x 1.4 |

Environmental & Export Classifications

| Pb (Lead) Free | No |

| HTS (US) | 8542320070 |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) |

Product Attributes

| Lead Count (#) | 128 |

| Pb (Lead) Free | No |

| Carrier Type | Reel |

| Architecture | Bi-directional |

| Bus Width (bits) | 36 |

| Core Voltage (V) | 5 |

| Density (Kb) | 512 |

| Family Name | Triple-Bus FIFO |

| Function | Bus Matching |

| I/O Frequency (MHz) | 1 - 1 |

| I/O Type | 5.0 V TTL |

| Interface | Synchronous |

| Length (mm) | 20 |

| MOQ | 1000 |

| Moisture Sensitivity Level (MSL) | 3 |

| Organization | 8K x 36 x 2 |

| Package Area (mm²) | 280.0 |

| Pb Free Category | e0 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 20.0 x 14.0 x 1.4 |

| Pkg. Type | TQFP |

| Qty. per Carrier (#) | 0 |

| Qty. per Reel (#) | 1000 |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Temp. Range | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 14 |

Resources for 723676

Description

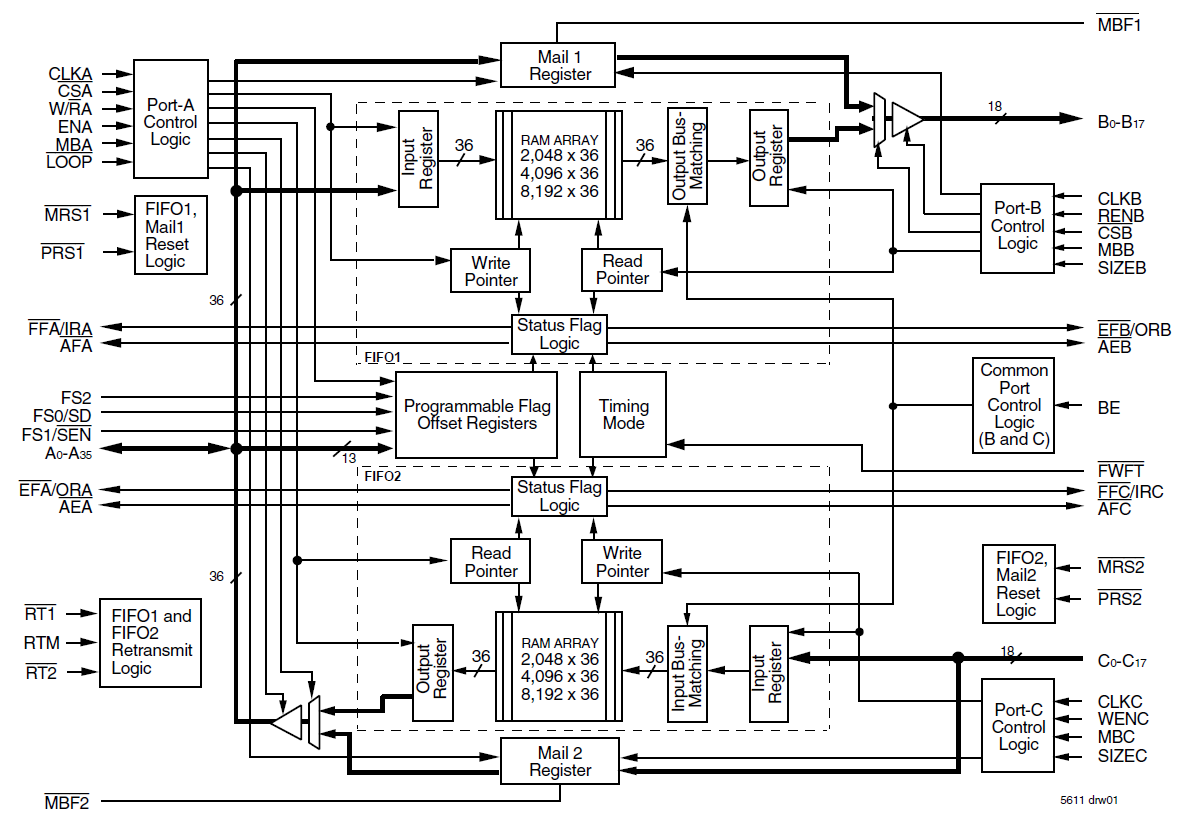

The 723676 is a 8K x 36 x 2 Triple Bus sync FIFO memory has two independent dual-port SRAM FIFOs on board each chip that can buffer data between a bidirectional 36-bit bus and two unidirectional 18-bit buses. FIFO data can be read and written using either 18-bit or 9-bit formats with a choice of Big- or Little-Endian configurations. Communication between each port may bypass the FIFOs via two mailbox registers. This device can operate in the IDT Standard mode or the first word fall through mode.