Overview

Description

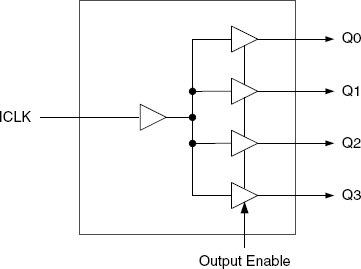

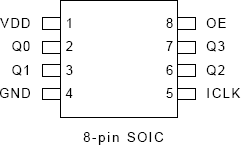

The 553 is a low skew, single input to four output, clock buffer. Part of Renesas' ClockBlocks™ family, this is our lowest skew, small clock buffer. See the 552-02 for a 1 to 8 low skew buffer. For more than eight outputs, see the MK74CBxxx Buffalo™ series of clock drivers. Renesas makes many non-PLL and PLL based low skew output devices as well as Zero Delay Buffers to synchronize clocks. Contact us for all of your clocking needs.

Features

- Extremely low skew outputs (50 ps maximum)

- Packaged in 8-pin SOIC

- Pb (lead) free package

- Low power CMOS technology

- Operating voltages of 2.5 V to 5 V

- Output Enable pin tri-states outputs

- 5 V tolerant input clock

- Commercial (0 to +70°C) and Industrial (-40 to +85°C) temperature ranges available

Comparison

Applications

Design & Development

Support

Support Communities

Support Communities

-

RSK-RZa1H linux RTC problem

Hi, want to use RTC of this processor, but I am getting VBAT pin in RTC module. I am not getting details about power supply of RTC. Can anyone guide me to do it. Thanks & Regards, Awadhesh

Jul 7, 2015 -

Binary mode stuck with repeat +++, Codeless. (6.380.18.63)

Hi,Im using two DA14531MOD devices, both using codeless (6.380.18.63). I have initially both connected and in Binary mode, then i power off one of the device. The other device starts spitting +++ sequence on repeat. if i dont respond quickly wth AT, it just keeps spitting +++ on ...

Jul 12, 2025 -

CANFD Register Setting Usage — RH850/F1KM-S2

In the sample project Y-ASK-RH850F1KM-S4-V3_sample_V1011. if the register RCFDCnCFDTMSTSp for channel 3 uses p = 96, shouldn't the corresponding register for channel 4 use p = 128 instead?2. In the configuration table, the third column corresponds to the register RCFDCnCFDGAFLP0_j. According to the ...

Jul 16, 2025