Overview

Description

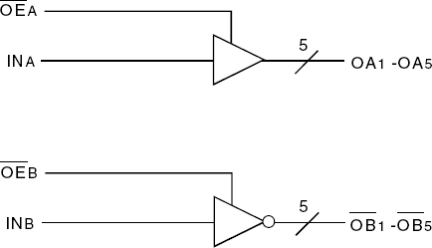

The 74FCT810T is a dual bank inverting/non-inverting clock driver built using advanced dual metal CMOS technology. It consists of two banks of drivers, one inverting and one non-inverting. Each bank drives five output buffers from a standard TTL-compatible input. The FCT810T has a low output skew, pulse skew, and package skew. Inputs are designed with hysteresis circuitry for improved noise immunity. The outputs are designed with TTL output levels and controlled edge rates to reduce signal noise. The part has multiple grounds, minimizing the effects of ground inductance.

Features

- 0.5micron CMOS technology

- Guaranteed low skew < 600ps (max.)

- Very low duty cycle distortion < 700ps (max.)

- Low CMOS levels

- TTL-compatible inputs and outputs

- TTL level output voltage swings

- High drive: -32mA IOH, +48mA IOL

- Two independent output banks with 3-state control: – One 1:5 inverting bank – One 1:5 non-inverting bank

- Available in QSOP, SSOP, and SOIC packages

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters: