Overview

Description

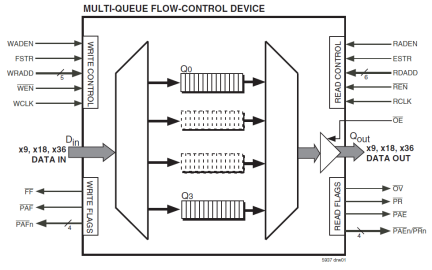

The 72V51256 multi-queue flow-control device is a single chip within which between 1 and 4 discrete FIFO queues can be setup. All queues within the device have a common data input bus, (write port) and a common data output bus, (read port). Data written into the write port is directed to a respective queue via an internal de-multiplex operation, addressed by the user. Data read from the read port is accessed from a respective queue via an internal multiplex operation, addressed by the user.

Features

- Total Available Memory = 2,359,296 bits

- Available Memory in blocks of 256 x 36

- ?Independent Read and Write access per

- ?100% Bus Utilization, Read and Write on every clock cycle

- ?166 MHz High speed operation (6ns cycle time)

- ?3.7ns access time

- ?Individual, Active queue flags (OV, FF, PAE, PAF, PR)

- ?Global Bus Matching - (All Queues have same Input Bus Width and Output Bus Width)

- ?User Selectable Bus Matching Options: - x36in to x36out - x18in to x36out - x9in to x36out - x36in to x18out - x36in to x9out

- ?FWFT mode of operation on read port

- ?JTAG Functionality (Boundary Scan)

- ?Available in a 256-pin PBGA package

- ?Industrial temperature range (-40C to +85C) is available

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters: