Overview

Description

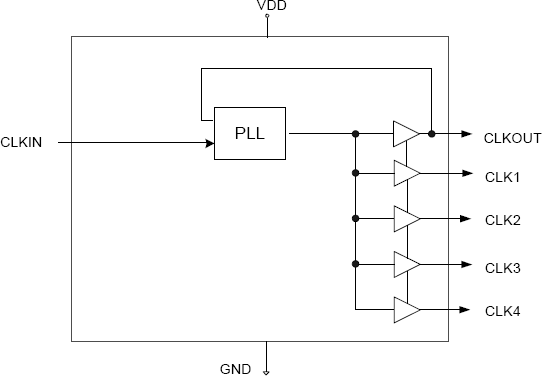

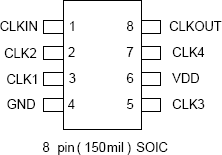

The 2305 is a low phase noise, high-speed PLL based, low-skew zero delay buffer. Based on the Renesas proprietary low jitter Phase Locked Loop (PLL) techniques, the device provides four low skew outputs at speeds up to 133 MHz at 3.3 V. The outputs can be generated from the PLL (for zero delay), or directly from the input (for testing), and can be set to tri-state mode or to stop at a low level. The PLL feedback is on-chip and is obtained from the CLKOUT pad. The 2305 is available in two different versions. The 2305-1 is the base part. The 2305-1H is a high drive version with faster rise and fall times.

Features

- Clock outputs from 10 to 133 MHz

- Zero input-output delay

- Four low skew (<250 ps) outputs

- Device-to-device skew <700 ps

- Full CMOS outputs with 25 mA output drive capability at TTL levels

- 5 V tolerant CLKIN

- Tri-state mode for board-level testing

- Advanced, low power, sub-micron CMOS process

- Operating voltage of 3.3 V

- Industrial temperature range available

- Packaged in 8-pin SOIC

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Support

Support Communities

Support Communities

-

about IDT2305

I have a few questions about the document on page 6 of the IDT2305 data sheet, "For designs utilizing zero I/O Delay, all outputs including CLKOUT must be equally loaded. Even if the output is not used, it must have a capacitiveload equal to that on the other ...

Dec 16, 2024