Renesas offers a wide variety of clocking products. Some of these products are optimized for the specific requirements of their target applications. In their target application, these products perform better and are easier to use than general-purpose clock parts. Renesas has clock generation and distribution products designed specifically for Network Synchronization, IEEE 1588, Synchronous Ethernet, PCI Express, Intel processors, Real-Time Clocks, RF, JESD204B/C, and Spread Spectrum applications.

Product Selector: Application-Specific Clocks

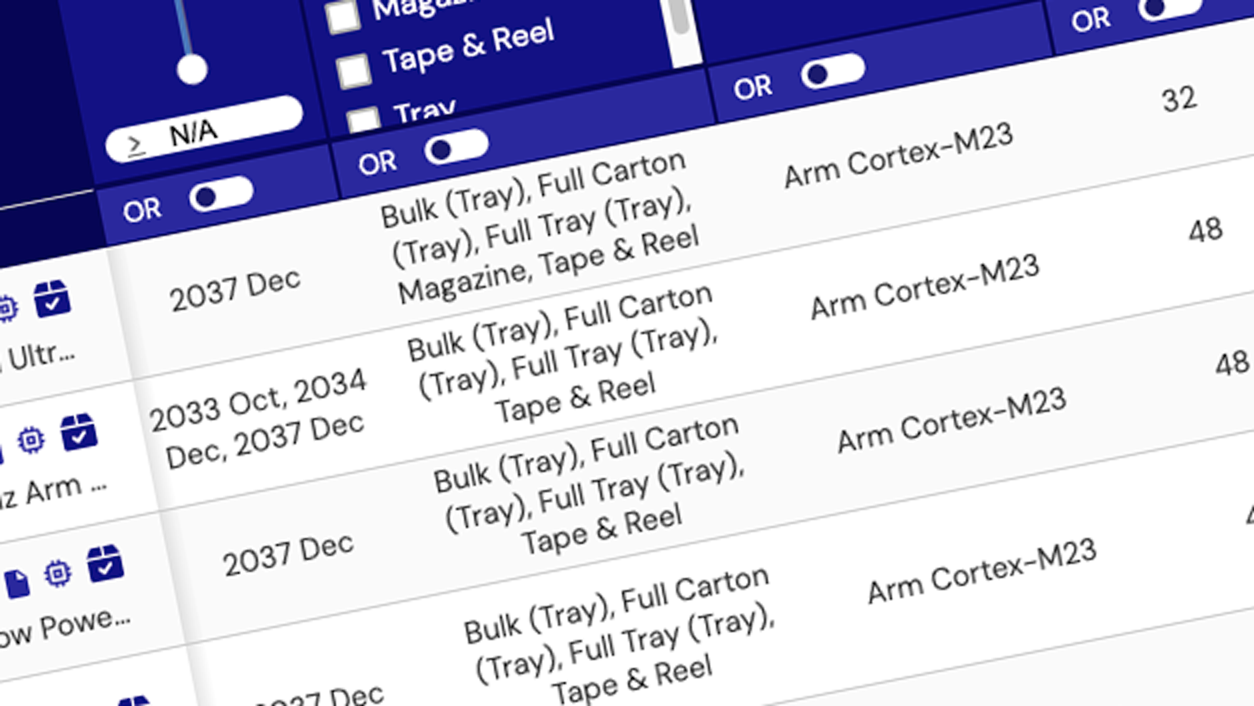

Explore our catalog of products through our parametric product selector tool. Compare specifications across various parameters to find the right part for your design.

Product SelectorVideos & Training

This video introduces the industry’s first fully-integrated synchronizer for 5G enhanced common public radio interface (eCPRI) radio synchronization.