Overview

Description

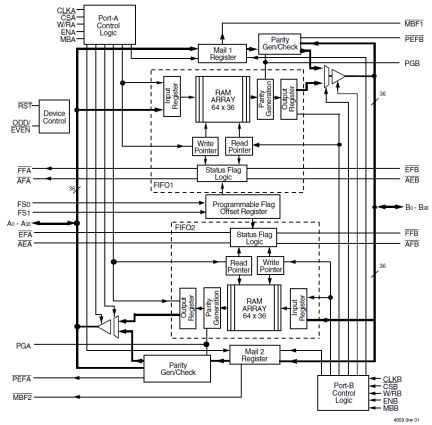

The 72V3612 is a 3.3V version of the 723612. Two independent 64 x 36 dual-port SRAM FIFOs on board the chip buffer data in opposite directions. Communication between each port can bypass the FIFOs via two 36-bit mailbox registers. The enables for each port are arranged to provide a simple bi-directional interface between microprocessors and/or buses with synchronous control.

Features

- Supports clock frequencies up to 83 MHz

- Fast access times of 8ns

- Free-running CLKA and CLKB can be asynchronous or coincident

- Mailbox bypass Register for each FIFO

- Programmable Almost-Full and Almost-Empty Flags

- Microprocessor interface control logic

- Passive parity checking on each port

- Available in 132-pin PQF and 120-pin TQFP packages

- Industrial temperature range (–40C +85C) is available

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters: