# Thermal Device Analysis and Design Considerations

# **Application Note**

80B8030\_AN002\_03

August 5, 2009

6024 Silver Creek Valley Road San Jose, California 95138

Telephone: (408) 284-8200 • FAX: (408) 284-3572

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. ("IDT") reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright  $^{\odot}$  2009 Integrated Device Technology, Inc. All Rights Reserved.

The IDT logo is registered to Integrated Device Technology, Inc. IDT and CPS are trademarks of Integrated Device Technology, Inc.

"Accelerated Thinking" is a service mark of Integrated Device Technology, Inc.

# 1. Thermal Device Analysis and Design Considerations

This document provides guidance in performing a thermal analysis and determining whether heat dissipation assistance is required for the IDT Semiconductor products.

This document discusses the following:

- "Overview" on page 3

- "Heat Movement" on page 4

- "Heat Sink Criteria" on page 6

- "Thermal Management" on page 7

- "FCBGA Thermal Model" on page 10

- "Physical Requirements for Heat Sinks" on page 12

# **Revision History**

#### 80B8030 AN002 03, Formal, August 2009

This document has been updated to reflect IDT formatting. There have been no technical changes.

#### 80B8030\_AN002\_02, Formal, November 2007

The Maximum Junction Temperature in Table 1 was changed from 120°C to 125°C.

#### 80B8030\_AN002\_01, Formal, April 2007

This was the first version of this document.

#### 1.1 Overview

IDT offers a large selection of semiconductor products in a variety of packages. Each device may require a different thermal solution depending upon the application, board size, and system thermal requirements. In some cases, a heat sink may be required to maintain junction temperatures at, or below, specified maximum values.

When using a heat sink it is important that attachment techniques and thermal requirements be critically analyzed to ensure reliability. Factors to be considered include: surface preparations, selection of thermal interface materials, curing process, shock and vibration requirements, and thermal expansion coefficients.

The analysis and formulas in this document can be used for any IDT device, however the Serial RapidIO Switch Tsi57x (which includes both the Tsi574 and Tsi578) has been chosen as an example for thermal analysis.

Each design should be individually analyzed to ensure that a reliable thermal solution is achieved.

#### 1.2 Heat Movement

IDT devices, like most high-performance devices, dissipate some thermal energy during normal operation. The high-level of functional integration and high operating frequency can have an effect on the silicon junction temperature (Tj) compared with a less integrated and lower frequency device. To ensure proper operation and device reliability, the silicon junction temperature must not exceed the maximum junction temperature specification.

Under typical operating conditions, system level thermal management may be needed to assist with dissipating the heat away from the chip package. In the case where assistance is required, a passive heat sink provides a reliable and cost effective method for removing the excess heat from the chip package. The size and shape of the heat sink depends on the operating conditions of the device and the characteristics of the system within which it operates.

#### 1.2.1 FCBGA Packaging

In the Tsi57x Flip Chip Ball Grid Array (FCBGA) package, the package case is the top of the silicon and the silicon chip is exposed. The heat sink is separated from the device by a layer of interface material. Underneath the interface material is the device, the ceramic substrate, solder balls, and the printed-circuit board (PCB).

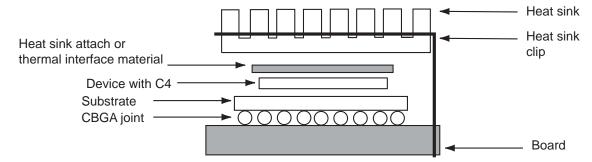

Figure 1 shows a FCBGA device attached to a PCB with an attached heat sink.

Figure 1: FCBGA Exploded Cross-sectional View

#### 1.2.2 Heat Sink Heat Transfer Path and Heat Flow

When a heat sink is attached to a device, the primary heat transfer path is as follows:

- 1. Heat generated by the active devices in the silicon chip is conducted through the silicon

- 2. Heat is conducted through the heat sink attached material

- 3. Heat is conducted to the heat sink itself, where it is removed by natural or forced-air convection

#### 1.2.2.1 Heat Flow

Heat flows through the device, the heat sink, and the board at differing rates.

#### Silicon Heat Flow

The rate of heat flow from the silicon chip through the package substrate to the printed circuit board is not significant in a flip-chip package in comparison to the heat flow to the heat sink and is not regarded as the primary path. Heat generated by the silicon chip is also transferred to the package so the temperature of the package also rises.

#### Heat Sink Heat Flow

The portion of the power that is dissipated by the heat sink must first propagate from the device through the heat sink thermal interface material joint. The thermal resistance of the thermal interface material joint can vary depending on the type of material used, such as thermal epoxy, thermal grease, or double-sided adhesive pads and the contact pressure of the heat sink bearing down on the device.

The rate at which the heat is transferred from the heat sink to the ambient air depends on the surface area of the heat sink and the velocity of the air passing through the heat sink. The rate of heat flow from the heat sink to the ambient air is not linear with the speed of the airflow as the characteristics of the air flow changes with velocity. The behavior of the heat sink must be validated with testing to ensure that the correct heat sink design has been selected for the environmental conditions.

#### **Board Heat Flow**

The heat dissipation through the board material depends largely on the number of power and ground layers inside the board and the amount of heat dissipated into the board from other devices soldered to it.

#### 1.3 Heat Sink Criteria

The following factors dictate the need for a heat sink in a board design:

- Thermal Conditions

- Ambient Environment

#### 1.3.1 Thermal Conditions

Thermal conditions include power dissipation, board layout, and air flow.

#### 1.3.1.1 Power Dissipation

The device's power dissipation and its thermal conductivity to the surrounding ambient environment determines the need for a heat sink. If the device is cool enough it may not need the heat sink. Whether a heat sink is required is defined by the temperature difference between the maximum junction temperature, the ability of the package to radiate heat into the ambient air, and the ambient temperature.

#### 1.3.1.2 Board Layout

The board layout impacts the effectiveness of the heat removal from the device and determines if a heat sink is required. The size and type of heat sink is also be defined by the proximity to other heat generating devices. The board layout also affects the efficiency of the heat sink if the heat sink is placed in an air-flow shadow behind a larger device or heat sink.

#### 1.3.1.3 Air Flow

Air flow across the device is a factor in heat sink requirement analysis. If the board is in still air, it must be determined if the radiated heat by all of devices in the chassis can escape without excessively elevating the temperature of adjacent devices. If there is an air flow directed across the printed circuit board, it must be ensured that the heat sink can access a large enough share of the moving air to perform its job effectively. Increasing the velocity of the air flowing across the printed circuit board may not be the solution if some of the devices are in the shadow of others in the air flow. The increase in velocity may actually cause the device in the shadow to become elevated in temperature because the air turbulence that it enjoyed at a lower but insufficient air flow, has moved further away because of the increased airflow velocity.

#### 1.3.2 Ambient Environment

Ambient environment factors must considered when analyzing the need for a heat sink. Ambient factors are both mechanical and chemical. Mechanical considerations include shock, vibration, and thermally induced stresses. Chemical considerations include environmental restrictions like thermal range, outgassing, flammability, and the acceptability for use by governing specifications.

# 1.4 Thermal Management

The Tsi57x devices are manufactured and tested to meet a commercial package temperature range of  $0^{\circ}$ C to  $+70^{\circ}$ C and an industrial range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. Thermal management must be used to keep the die junction temperature below the specified  $120^{\circ}$ C.

Tsi57x package thermal characteristics are shown in Table 1.

Table 1: Tsi57x Thermal Characteristics

| Measurement                            | Result                                                                                                                                                                                                                                               |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum Junction Temperature           | 125°C                                                                                                                                                                                                                                                |

| Theta <sub>ja</sub> (junction to air)  | 18.77 °C/W (with no Heat sink and no air flow)                                                                                                                                                                                                       |

| Theta <sub>jc</sub> (junction to case) | 0.09 °C/W In a FCBGA package, where the backside of the die is the top of the package assembly, Theta <sub>jc</sub> describes the thermal resistance from the transistor junctions inside the die to the surface of the exposed backside of the die. |

| Theta <sub>jb</sub> (junction to ball) | 10.96 °C/W                                                                                                                                                                                                                                           |

For the Tsi57x devices, the configuration of link speed and the number of links in use determine the total power dissipation. Refer to the "Calculation Equation" on page 8 for more information on calculated power dissipation and junction temperature.

#### 1.4.1 Junction Temperature

To determine whether a heat sink is necessary, the junction temperature must be calculated. The following sections show the equation for calculation, an example calculation, and different junction temperatures for the Tsi57x device.

#### 1.4.1.1 Calculation Equation

The junction temperature may be calculated using the formula:

$$T_i = T_a + (P - P_{pcb}) * Theta_{ia}$$

Where.

$T_i$  = Calculated junction temperature

$T_a$  = Ambient temperature around the device

P = Power consumed

$P_{pcb}$  = Thermal resistance from the ball to board and board to ambient air.

Theta<sub>ja</sub> = Thermal resistance from the die junction to the ambient air

#### 1.4.1.2 Calculation Example

In this example, it is assumed that there is no dissipation through the board (because there are no details about the board size, number of layers and density of other components on the board).

Using the thermal resistance data from Table 1 and the power consumption values in Table 2 for a Tsi578 in 4x mode and eight active links, we can find the maximum junction temperature at a given ambient. Using an ambient temperature of 70°C, a power dissipation of 5.11 W and a thermal resistance of junction-to-ambient figure of 18.77 °C/W.

$$T_i = 70 + 5.11 * 18.77 = 166$$

°C

The resulting calculation yields a junction temperature of 166°C, which is greater than the maximum specified junction temperature of 120°C. It can be concluded then that a heat sink is required.

#### 1.4.1.3 Calculated Junction Temperatures for the Tsi57x

Table 2 shows both Tsi574 and Tsi578 devices in different configurations. By repeating the calculation in "Calculation Example" on page 8 for each power consumption value, the temperature for each condition was obtained. Because the power dissipation varies depending on the device configuration, the junction temperature also varies. Instances where the junction temperature exceeds 120°C, and require a heat sink, are shaded in grey.

Table 2: Power and Tj in Typical Configurations

| Line Rate – Measured Total Power |                          |                                                |             |                                   |             |                                    |             |  |

|----------------------------------|--------------------------|------------------------------------------------|-------------|-----------------------------------|-------------|------------------------------------|-------------|--|

| Link Speed                       |                          | 1.25 GBaud (T <sub>a</sub> =70 <sup>o</sup> C) |             | 2.5 GBaud (T <sub>a</sub> =70 °C) |             | 3.125 GBaud (T <sub>a</sub> =70 ℃) |             |  |

| Device                           | Mode                     | Power                                          | Temperature | Power                             | Temperature | Power                              | Temperature |  |

| Tsi574                           | 4x mode with<br>4 links  | 1.84 W                                         | 104.5ºC     | 2.35 W                            | 114.1°C     | 2.74 W                             | 121.4ºC     |  |

| Tsi574                           | 1x mode with<br>8 links  | 1.74 W                                         | 102.7°C     | 2.23 W                            | 111.9°C     | 2.59 W                             | 118.6ºC     |  |

| Tsi578                           | 4x mode with<br>8 links  | 3.32 W                                         | 132.3°C     | 4.34 W                            | 151.5ºC     | 5.11 W                             | 166°C       |  |

| Tsi578                           | 1x mode with<br>16 links | 3.23 W                                         | 130.6°C     | 4.09 W                            | 146.8°C     | 4.84 W                             | 161ºC       |  |

### 1.5 FCBGA Thermal Model

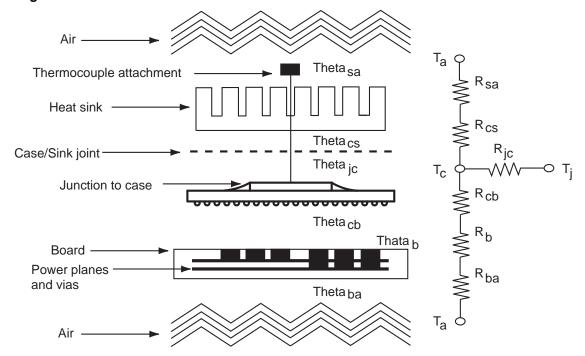

The thermal model with a heat sink can found using an equation. Figure 2 shows a typical heat sink on a FCBGA. The equation parameters shown in "Thermal Model Equation" on page 11 are also illustrated in the figure.

Figure 2: Thermal Model with Heat Sink

#### 1.5.1 Thermal Model Equation

The thermal model equation is:

Theta<sub>ja</sub> = Theta<sub>jc</sub> +

$$\frac{1}{1}$$

$$\frac{1}{1} + \frac{1}{1}$$

Theta<sub>cs</sub> + Theta<sub>sa</sub> Theta<sub>cb</sub> + Theta<sub>b</sub>

Where,

Theta<sub>ia</sub> = Thermal resistance from the die junction to the ambient air

Theta<sub>ic</sub> = Thermal resistance of the silicon from to the die junction to the case (backside of the die)

Theta<sub>cs</sub> = Thermal resistance of the heat sink attach (interface material) from the case to the heat sink

Theta<sub>sa</sub> = Thermal resistance of the heat sink to the ambient air

Theta<sub>ib</sub> = Thermal resistance from the die junction to the solder balls

Theta<sub>cb</sub> = Thermal resistance of the solder balls to the board

Theta<sub>b</sub> = Thermal resistance of the board

Theta<sub>ba</sub> = Thermal resistance of the board to the ambient air

#### 1.5.1.1 Calculation Assumptions

Using the equation, certain assumptions must be factored into the thermal model. The following equation assumes board size, board layout, and the number of layers on the board:

$Tj = Ta + P * (Theta_{jc} + Theta_{cs} + Theta_{sa})$  assuming  $(Theta_{jb} + Theta_{cb} + Theta_{b} + Theta_{ba}) = 0$ , since  $Theta_{jb}$  is 121.7 times larger than  $Theta_{jc}$ , board size, board layout and number of layers are unknown.

The choice of the heat sink largely depends board factors (as shown in the "Thermal Model Equation Example" on page 11). Other factors that can affect heat dissipation include board design/materials and the case to sink attachment method. The mass of a heat sink may impose a relatively long thermal Time Constant of the case/heat sink combination can slow down the response time of the thermal solution to any power peaks that may occur. To validate proper operation of the heat sink, a small hole should be drilled in the center of the sink to place a miniature thermocouple directly on the case (center top surface) to measure the actual case temperature under system's maximum expected operating conditions.

#### 1.5.1.2 Thermal Model Equation Example

In this example, the following operating conditions are assumed:

- $P_a = 5.11 \text{ W}$

- Average Power Dissipated by the device

- $T_a = 70 \, ^{\circ}C$

- Ambient air temperature

- Theta<sub>cs</sub> = 0.5 °C/W

- Interface material (in this case, thermal epoxy adhesive)

- $T_i = 120 \, ^{\circ}C$

- Maximum Junction temperature

Using the formula  $Tj = Ta + P * (Theta_{jc} + Theta_{cs} + Theta_{sa})$  maximum heat sink to air thermal resistance  $Theta_{sa}$  can be calculated that will maintain the case temperature below Tj for the operating conditions specified above.

- 1.  $Tj Ta = P * (Theta_{ic} + Theta_{cs} + Theta_{sa})$

- 2.  $(Tj Ta)/P = (Theta_{ic} + Theta_{cs} + Theta_{sa})$

- 3. Theta<sub>sa</sub> = (Tj Ta)/P (Theta<sub>ic</sub> + Theta<sub>cs</sub>)

- 4. Theta<sub>sa</sub> = (120-70)/5.11 (0.1+0.5)

- 5. Theta<sub>sa</sub>=  $9.2 \, ^{\circ}\text{C/W}$

Based on the calculations, a heat sink with a maximum sink to air thermal resistance of 9.2 °C/W must be chosen for power dissipation of 5.11 watts.

# 1.6 Physical Requirements for Heat Sinks

The following sections describe physical considerations for the mounting of a heat sink.

#### 1.6.1 Heat Sink Mounting

The preferred method for mounting a heat sink is by mechanical attachment to a PCB. If an adhesive attach is used, IDT recommends a pressure-sensitive adhesive, such as Loctite 384 with an activator. Adhesive should only be used for small mass heat sinks.

IDT does not recommend a clip-to-package substrate approach for plastic laminate substrates without overmold due to the stresses developed by pressing down on the die while lifting up on the edges of the package substrate.

#### 1.6.2 Interface Material

For applications where the heat sink is required, a thermal interface material at the die-to-heat sink interface can minimize thermal contact resistance. The thermal performance is different for the three thin-sheet interface materials (silicone, graphite/oil, floroether oil) when used with a bare joint, or a joint with thermal grease as a function of contact pressure. The decision to use one material over another is based on cost of the materials and the labour to implement the solution on each board assembly manufactured.

These thermal interface materials' performance improves with increasing contact pressure by filling in the imperfections on the surfaces of the die and heat sink. Silicon die are fragile, and any heat sink attach scheme must accommodate structural compliance to avoid damage to the die. The use of thermal grease and a graphite/oil sheet significantly reduces interface resistance and is the desired solution as opposed to increasing the contact pressure.

The bare joint results in a thermal resistance approximately seven times greater than that of a thermal grease joint. These results may be used as a guide to show improvements that thermal interface materials offer over bare joints.

#### 1.6.2.1 FCBGA Package Heat Sink Mounting Force

Some heat sink mounting methods generate a compressive load on the package. The Tsi57x FCBGA package the maximum force applied to the package should be limited to 5 gm / BGA ball.

The maximum force applied to the package assumes that the board is supported to prevent any flexing or bowing.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.