-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

IEEE 1588 and Synchronous Ethernet Clocks (SyncE)

The Renesas Digital PLLs (DPLLs) for IEEE 1588 and synchronous Ethernet are designed for synchronization over packet switched networks. For IEEE 1588 applications, the embedded Digitally Controlled Oscillators (DCOs) can be used as low-jitter synthesizers for IEEE 1588 clock recovery algorithms. For synchronous Ethernet applications, the DPLLs comply with ITU-T recommendations for (synchronous Ethernet Equipment Clocks (EECs); these devices also comply with SONET/SDH, PDH and TDM synchronization requirements. The Renesas DPLLs can be switched between IEEE 1588 DCO and SyncE modes; and they provide capabilities such as selectable loop filters, holdover, hitless reference switching, phase slope limiting, and clock redundancy.

Download the Altera and IDT Synchronous Ethernet Solution for ITU-T G.8262 white paper

About IEEE 1588

IEEE 1588 is a precision time protocol (PTP) used to synchronize clocks throughout a computer network. On a local area network, it achieves clock accuracy in the sub-microsecond range, making it suitable for measurement and control systems. The IEEE 1588 standard defines a master-slave architecture for clock distribution, consisting of one or more network segments, and one or more clocks. Renesas addresses IEEE 1588 clocking needs with an industry-leading portfolio of high-performance solutions.

About Synchronous Ethernet (SyncE)

Synchronous Ethernet is an ITU-T standard for computer networking that defines how clock signals are transferred over the Ethernet physical layer. The purpose of synchronous Ethernet is to provide a synchronization signal to various resources over a network. The synchronous Ethernet signal is transmitted over the Ethernet physical layer and should be traceable to an external clock. Applications include routers, multi-service switching platforms, Passive Optical Networks (PON), and Digital Subscriber Line Access Multiplexers (DSLAMs). As the only supplier with all of the different timing components to provide complete solutions, Renesas is uniquely positioned to meet the needs of communication equipment suppliers and offer compelling solutions for all timing fabric architectures.

Product Selection Table

Application |

Clock Support |

Channels (#) |

Inputs (#) |

Diff. Inputs |

Input Freq (MHz) |

Output Freq Range (MHz) |

Phase Jitter Typ RMS (ps) |

Diff. Outputs |

Outputs (#) |

Pkg. Type |

Lead Count (#) |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Part Number | |||||||||||||

| System Synchronizer for IEEE 1588 - Six Channels | Low-cTE Timing Card, PTP Timing Card, SETS | G.813, G.8262, G.8262.1, G.8273.2, GR-253-CORE, GR-1244-CORE | 6 | 8 | 4 | 0.0000005 - 1000 | 0.0000005 - 1000 | 0.1 | 14 | 24 | CABGA | 144 | |

| VCXO Jitter Attenuator & FemtoClock® Multiplier | Port Synchronizer | 1 | 2 | 2 | 0.008 - 155.52 | 25 - 312.5 | 0.3 | 2 | 2 | VFQFPN | 32 | ||

| System Synchronizer for IEEE 1588 - Eight Channels | Low-cTE Timing Card, PTP Timing Card, SETS | G.813, G.8262, G.8262.1, G.8273.2, GR-253-CORE, GR-1244-CORE | 8 | 16 | 8 | 0.0000005 - 1000 | 0.0000005 - 1000 | 0.15 | 12 | 24 | CABGA | 144 | 54.23 |

| System Synchronizer for IEEE 1588 - Four Channels | Low-cTE Timing Card, PTP Timing Card, SETS | G.813, G.8262, G.8262.1, G.8273.2, GR-253-CORE, GR-1244-CORE | 4 | 14 | 7 | 0.0000005 - 1000 | 0.0000005 - 1000 | 0.15 | 8 | 16 | VFQFPN | 72 | 35.53 |

| System Synchronizer for IEEE 1588 - Four Channels | Low-cTE Timing Card, PTP Timing Card, SETS | G.813, G.8262, G.8262.1, G.8273.2, GR-253-CORE, GR-1244-CORE | 4 | 4 | 2 | 0.0000005 - 1000 | 0.0000005 - 1000 | 0.15 | 4 | 8 | VFQFPN | 48 | 41.34 |

| System Synchronizer for IEEE 1588 - Two Channels | Low-cTE Timing Card, PTP Timing Card, SETS | G.813, G.8262, G.8262.1, G.8273.2, GR-253-CORE, GR-1244-CORE | 2 | 4 | 2 | 0.0000005 - 1000 | 0.0000005 - 1000 | 0.15 | 4 | 8 | VFQFPN | 48 | |

| System Synchronizer for IEEE 1588 - Four Channels | Low-cTE Timing Card, PTP Timing Card, SETS | G.813, G.8262, G.8262.1, G.8273.2, GR-253-CORE, GR-1244-CORE | 4 | 4 | 2 | 0.0000005 - 1000 | 0.0000005 - 1000 | 0.15 | 12 | 24 | VFQFPN | 72 | |

| Line Card Synchronizer for IEEE 1588 - Eight Channels | Low-cTE Line Card, PTP Line Card | 8 | 16 | 8 | 0.001 - 1000 | 0.0000005 - 1000 | 0.15 | 12 | 24 | CABGA | 144 | 43.8 | |

| Line Card Synchronizer for IEEE 1588 - Four Channels | Low-cTE Line Card, PTP Line Card | 4 | 14 | 7 | 0.001 - 1000 | 0.0000005 - 1000 | 0.15 | 8 | 16 | VFQFPN | 72 | 34.81 | |

| Line Card Synchronizer for IEEE 1588 - Four Channels | Low-cTE Line Card, PTP Line Card | 4 | 4 | 2 | 0.001 - 1000 | 0.0000005 - 1000 | 0.15 | 4 | 8 | VFQFPN | 48 | ||

| SETS for SyncE and OTN | SETS, System Synchronizer | G.813, G.8262, G.8262.1, GR-253-CORE, GR-1244-CORE | 4 | 8 | 4 | 0.001 - 1000 | 0.0000005 - 1000 | 0.15 | 12 | 24 | VFQFPN | 72 | |

| FemtoClock™ NG Universal Frequency Translator | Jitter Attenuator, Port Synchronizer | 1 | 2 | 2 | 0.008 - 875 | 0.008 - 1000 | 0.2 | 4 | 4 | VFQFPN | 40 | 9.551 | |

| FemtoClock™ NG Universal Frequency Translator | Jitter Attenuator, Port Synchronizer | 1 | 2 | 2 | 0.008 - 875 | 0.008 - 1000 | 0.35 | 4 | 4 | VFQFPN | 40 | 6.081 | |

| FemtoClock™ NG Universal Frequency Translator | Jitter Attenuator, Port Synchronizer | 1 | 2 | 2 | 0.008 - 875 | 0.008 - 1000 | 0.276 | 4 | 4 | VFQFPN | 40 | 5.795 | |

| FemtoClock NG Universal Frequency Translator (2-in/1-PLL/8-out) | Jitter Attenuator, Port Synchronizer | 2 | 2 | 4 | 0.008 - 875 | 0.008 - 1000 | 0.28 | 8 | 8 | VFQFPN | 56 | 9.973 | |

| FemtoClock NG Universal Frequency Translator (4-in/2-PLL/8-out) | Jitter Attenuator, Port Synchronizer | 2 | 4 | 4 | 0.008 - 875 | 0.008 - 1000 | 0.28 | 8 | 8 | VFQFPN | 72 | 12.73 | |

| FemtoClock NG Universal Frequency Translator (2-in/2-PLL/8-out) | Jitter Attenuator, Port Synchronizer | 2 | 2 | 2 | 0.008 - 875 | 0.008 - 1000 | 0.28 | 8 | 8 | VFQFPN | 56 | 12.99 | |

| FemtoClock™ NG 12-Output Clock Generator | Clock Generator | 1 | 2 | 2 | 5 - 1000 | 10.91 - 2500 | 0.095 | 11 | 12 | VFQFPN | 64 | ||

| FemtoClock™ NG 12-Output Clock Generator | Clock Generator | 1 | 2 | 2 | 5 - 1000 | 10.91 - 2500 | 0.089 | 11 | 12 | VFQFPN | 64 | 14.63 | |

| FemtoClock™ NG 12-Output Clock Generator | Clock Generator | 1 | 2 | 2 | 5 - 1000 | 10.91 - 2500 | 0.08 | 11 | 12 | VFQFPN | 64 | ||

| VersaClock® 7 Programmable Jitter Attenuator Family | Jitter Attenuator for PHY or Switches, Routers, Switches and more... |

G.8262, G.8262.1, T-TSC | 2 | 2 | 1 - 650 | 0.001 - 650 | 0.15 | 5, 8, 12 | 16, 24 | LGA | 32, 40, 48 | ||

| Radio Access Network Equipment Synchronizer - Six Channels | Centralized Unit (CU), Distributed Unit (DU), Radio Unit (RU) and more... |

6 | 10 | 5 | 0.001 - 1000 | 0.0000005 - 1000 | 0.15 | 12 | 24 | VFQFPN | 72 |

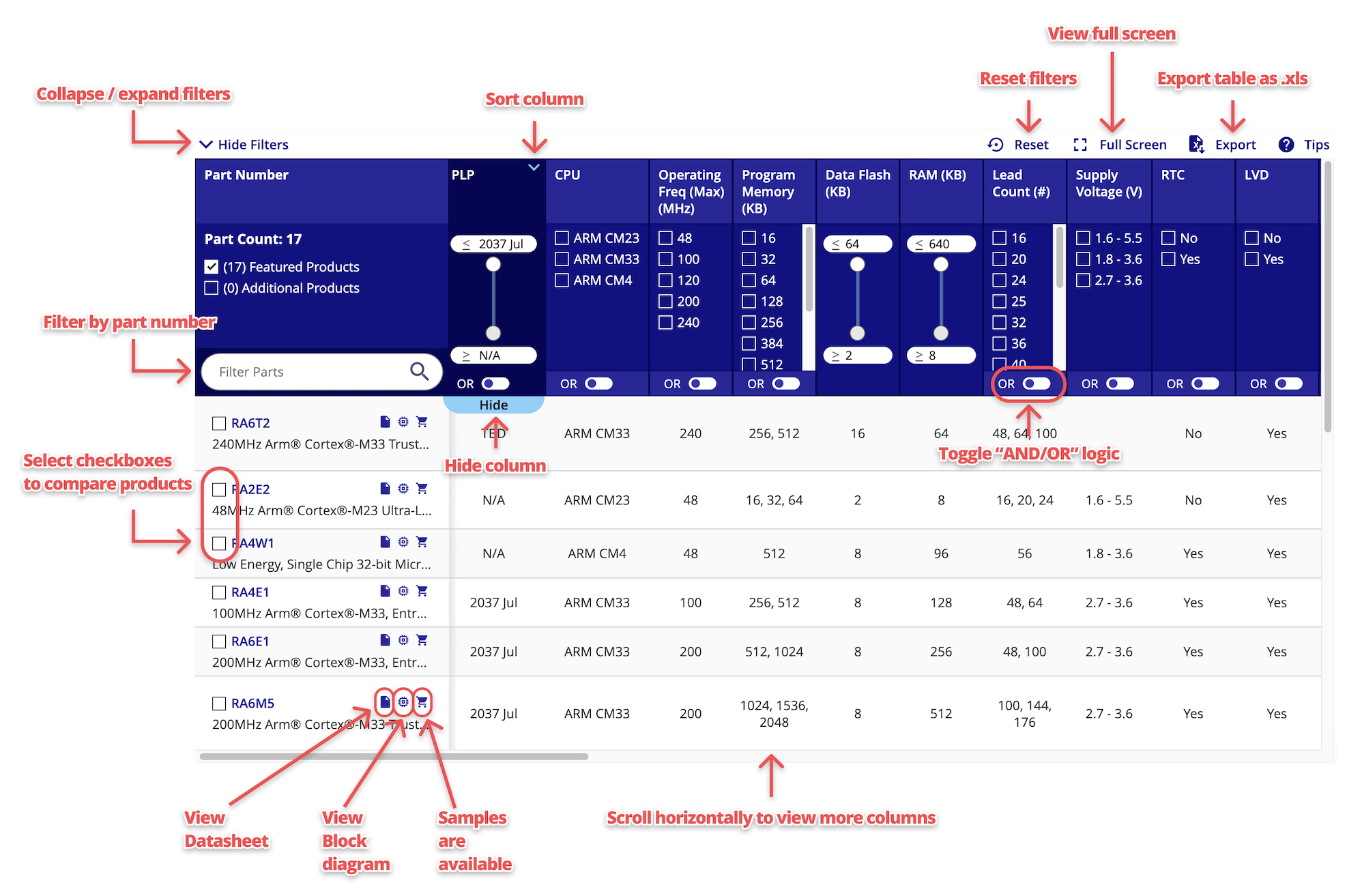

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Overview | PDF 1.31 MB | |

| Overview | PDF 263 KB | |

| White Paper | PDF 299 KB | |

3 items

|

||

Videos & Training

The ClockMatrix™ 2 family of devices are high-performance, precision timing solutions designed to simplify clock designs for applications with up to 800Gbps interface speeds. This second-generation family delivers improved performance with phase jitter as low as 88fs RMS. The highly integrated devices serve as full-function IEEE 1588 synchronization clocks and ultra-low jitter reference clocks for synchronous Ethernet PHYs with data rates up to 112Gbps PAM-4, reducing design complexity and bill of materials (BOM). Visit renesas.com/clockmatrix to learn more.