# RENESAS

# Overview

The 8A34013 is a port synchronizer for frequency and time/phase for equipment that uses packet-based and physical layer-based equipment synchronization.

The 8A34013 is a highly integrated device that provides tools to manage timing references, clock sources, and timing paths for IEEE 1588 and Synchronous Ethernet (SyncE) based clocks. The PLL channels can act independently as frequency synthesizers, jitter attenuators, Digitally Controlled Oscillators (DCO), or Digital Phase Lock Loops (DPLL).

# **Typical Applications**

- Core and access IP switches / routers

- Synchronous Ethernet equipment

- Telecom Boundary Clocks (T-BCs) and Telecom Time Slave Clocks (T-TSCs) according to ITU-T G.8273.2

- 10Gb, 40Gb, and 100Gb Ethernet interfaces

- Central Office Timing Source and Distribution

- Wireless infrastructure for 4.5G and 5G network equipment

# **Features**

- Four independent timing channels

- Each can act as a frequency synthesizer, jitter attenuator, Digitally Controlled Oscillator (DCO), or Digital Phase Lock Loop (DPLL)

- DPLL Digital Loop Filters (DLFs) are programmable with cut off frequencies from 17Hz to 22kHz

- Switching between DPLL and DCO modes is hitless and dynamic

- Generates output frequencies that are independent of input frequencies via a Fractional Output Divider (FOD)

- Each FOD supports output phase tuning with 1ps resolution

- 4 Differential / 8 LVCMOS outputs

- Frequencies from 0.5Hz to 1GHz (250MHz for LVCMOS)

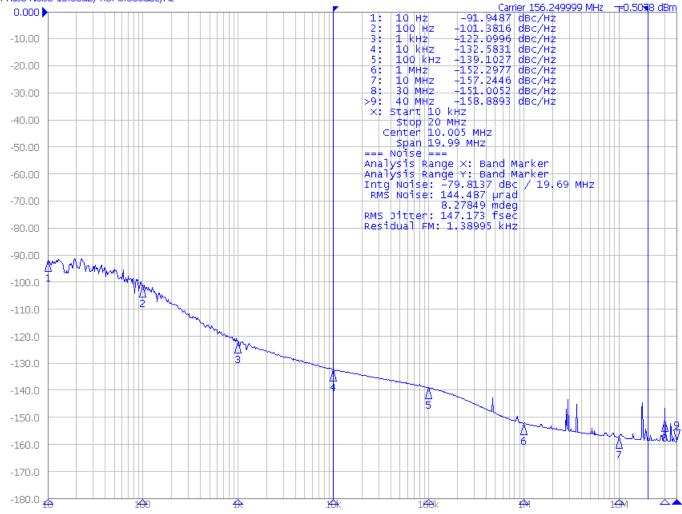

- Jitter below 150fs RMS (10kHz to 20MHz)

- LVCMOS, LVDS, LVPECL, HCSL, CML, SSTL, and HSTL output modes supported

- Differential output swing is selectable: 400mV / 650mV / 800mV / 910mV

- Independent output voltages of 3.3V, 2.5V, or 1.8V

- LVCMOS additionally supports 1.5V or 1.2V

- The clock phase of each output is individually programmable in 1ns to 2ns steps with a total range of ±180°

- 2 differential / 4 single-ended clock inputs

- Support frequencies from 1kHz to 1GHz

- Any input can be mapped to any or all of the timing channels

- · Redundant inputs frequency independent of each other

- Any input can be designated as external frame/sync pulse of PPES (pulse per even second), 1PPS (Pulse per Second), 5PPS, 10 PPS, 50Hz, 100Hz, 1 kHz, 2 kHz, 4kHz, and 8kHz associated with a selectable reference clock input

- Per-input programmable phase offset of up to  $\pm 1.638 \mu s$  in 1ps steps

- Reference monitors qualify/disqualify references depending on LOS, activity, frequency monitoring, and/or LOS input pins

- Loss of Signal (LOS) input pins (via GPIOs) can be assigned to any input clock reference

- Automatic reference selection state machines select the active reference for each DPLL based on the reference monitors, priority tables, revertive / non-revertive, and other programmable settings

- System APLL operates from fundamental-mode crystal: 25MHz to 54MHz or from a crystal oscillator

- System DPLL accepts an XO, TCXO, or OCXO operating at virtually any frequency from 1MHz to 150MHz

- DPLLs can be configured as DCOs to synthesize Precision Time Protocol (PTP) / IEEE 1588 clocks

- DCOs generate PTP based clocks with frequency resolution less than  $1.11\times 10^{-16}$

- DPLL Phase detectors can be used as Time-to-Digital Converters (TDC) with precision below 1ps

- Supports 1MHz I<sup>2</sup>C or 50MHz SPI serial processor ports

- Can configure itself automatically after reset via:

- Internal customer definable One-Time Programmable memory with up to 16 different configurations

- Standard external I<sup>2</sup>C EPROM via separate I<sup>2</sup>C Master Port

- 1149.1 JTAG Boundary Scan

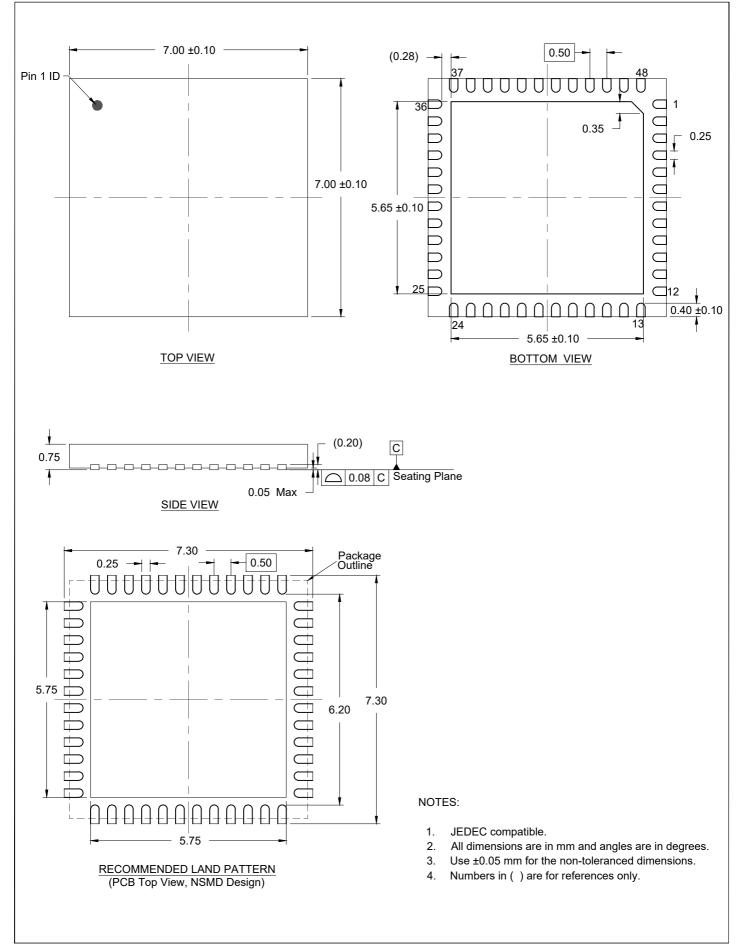

- 7 × 7 mm 48-VFQFPN package

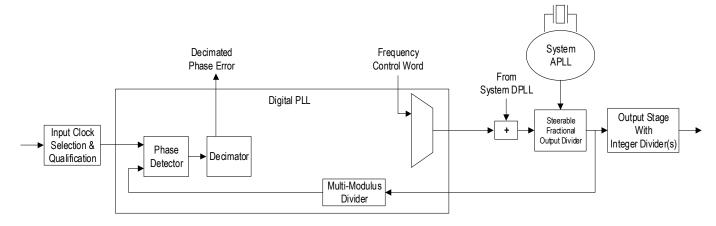

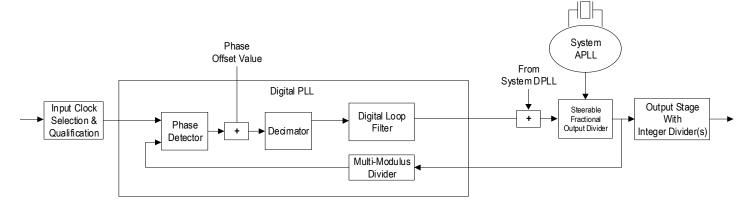

# Block Diagram<sup>[1]</sup>

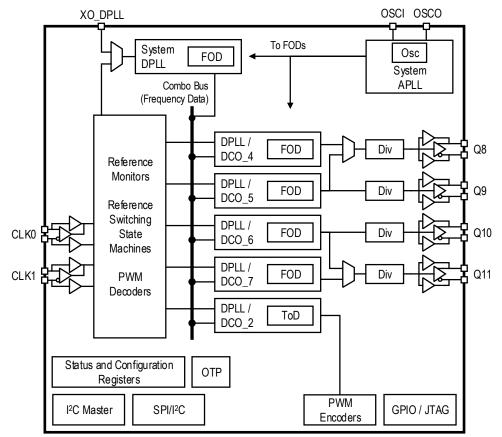

### Figure 1. Block Diagram

# Description

The 8A34013 is a port synchronizer for frequency and time/phase for equipment that uses packet based and physical layer based equipment synchronization. The 8A34011 is a highly integrated device that provides tools to manage timing references, clock sources, and timing paths for IEEE 1588 and Synchronous Ethernet (SyncE) based clocks. The PLL channels can act independently as frequency synthesizers, jitter attenuators, Digitally Controlled Oscillators (DCO), or Digital Phase Lock Loops (DPLL).

The 8A34013 supports multiple independent timing paths that can each be configured as a DPLL or as a DCO. Input-to-input, input-to-output, and output-to-output phase skew can all be precisely managed. The device outputs low-jitter clocks that can directly synchronize interfaces such as 100GBASE-R, 40GBASE-R, 10GBASE-R, and 10GBASE-W and lower-rate Ethernet interfaces; as well as SONET/SDH and PDH interfaces, and IEEE 1588 Time Stamp Units (TSUs).

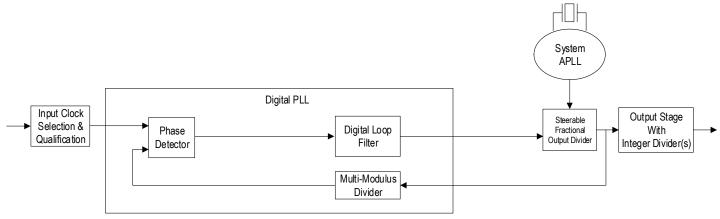

The internal System APLL must be supplied with a low phase noise reference clock with frequency between 25MHz and 54MHz. The output of the System APLL is used for clock synthesis by all of the Fractional Output Dividers (FODs) in the device. The System APLL reference can come from an external crystal oscillator connected to the OSCI pin or from an internal oscillator that uses a crystal connected between the OSCI and OSCO pins.

<sup>[1]</sup> This product is covered by one or more of the following patents: US 9,369,270, US 10,355,699, US 10,075,284, US 9,628,255, and US 9,479,182.

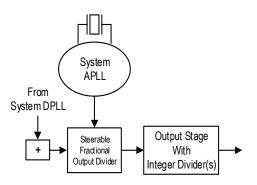

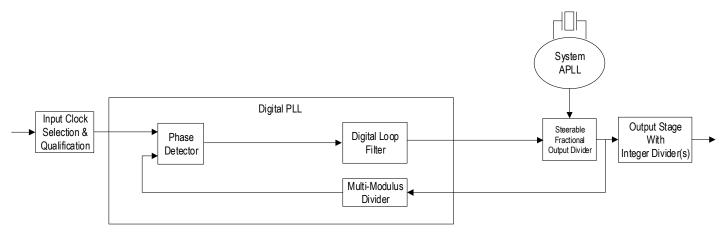

The System DPLL generates an internal system clock that is used by the reference monitors and other digital circuitry in the device. If the reference provided to the System APLL meets the stability and accuracy requirements of the intended application then the System DPLL can free run and a System DPLL reference is not required. Alternatively, the System DPLL can be locked to an external reference that meets the stability and accuracy requirements of the intended application. The System DPLL can accept a reference from the XO\_DPLL pin or via the reference selection mux.

The frequency accuracy/stability of the internal system clock determines the frequency accuracy/stability of the DPLLs in Free-Run mode and in Holdover mode; and it affects the wander generation of the DPLLs in Locked and DCO modes. When provided with a suitably stable and accurate system clock, the DPLLs meet the frequency accuracy, pull-in, hold-in, pull-out, noise generation, noise tolerance, transient response, and holdover performance requirements of ITU-T G.8262 synchronous Ethernet Equipment Clock (EEC) options 1 and 2.

The 8A34013 accepts up to two differential reference inputs and up to four single-ended reference inputs that can operate at common GNSS, Ethernet, SONET/SDH, PDH frequencies, and any input frequency from 1kHz to 1GHz (250MHz in single-ended mode). The references are continually monitored for loss of signal and for frequency offset per user-programmed thresholds. All of the references are available to all the DPLLs. The active reference for each DPLL is determined by forced selection or by automatic selection based on user programmed priorities, locking allowances, reference monitors, revertive and non-revertive settings, and LOS inputs.

The 8A34013 can accept a clock reference and an associated frame pulse or sync signal as a pair. DPLLs can lock to the clock reference and align the sync and clock outputs with the paired sync/frame input. The device allows any of the reference inputs to be configured as sync inputs that can be associated with any of the other reference inputs. The input sync signals can have a frequency of 1PPS (Pulse per Second), PPES (pulse per even second), 5PPS, 10 PPS, 50Hz, 100Hz, 1 kHz, 2 kHz, 4kHz, and 8 kHz. This feature enables any DPLL to phase align its frame sync and clock outputs with a sync input without the need to use a low bandwidth setting to lock directly to the sync input.

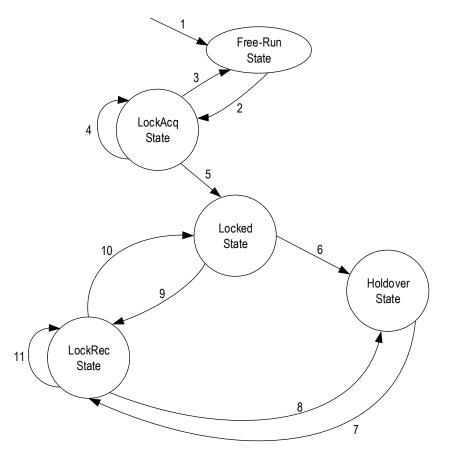

The DPLLs support four primary operating modes: Free-Run, Locked, Holdover, and DCO. In Free-Run mode the DPLLs synthesize clocks based on the system clock alone. In Locked mode the DPLLs filter reference clock jitter with the selected bandwidth. Additionally in Locked mode, the long-term output frequency accuracy is the same as the long-term frequency accuracy of the selected input reference. In Holdover mode, the DPLL uses frequency data acquired while in Locked mode to generate accurate frequencies when input references are not available. In DCO mode the DPLL control loop is opened and the DCO can be controlled by a PTP clock recovery servo running on an external processor to synthesize PTP clocks.

The DPLLs can be configured with a range of selectable filtering bandwidths from 17Hz to 22kHz for use in jitter attenuation and rate conversion applications.

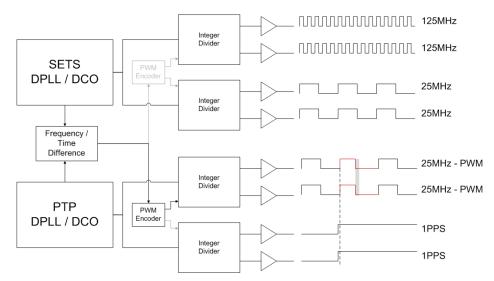

In Telecom Boundary Clock (T-BC) and Telecom Time Slave Clock (T-TSC) applications per ITU-T G.8275.2, two DPLLs can be used; one DPLL is configured as a DCO to synthesize PTP clocks and the other DPLL is configured as an EEC/SEC to generate physical layer clocks. Combo mode provides physical layer frequency support from the EEC/SEC to the PTP clock.

For applications per ITU-T G.8263, any DPLL can be configured as a DCO to synthesize packet-based clocks.

In Synchronous Equipment Timing Source (SETS) applications per ITU-T G.8264, any of the DPLLs can be configured as an EEC/SEC to output clocks for the T0 reference point and can be used to output clocks for the T4 reference point.

The 8A34013 generates up to four differential output clocks at any frequency from 0.5Hz to 1GHz. The differential outputs can support LVPECL, LVDS, HCSL, and CML. It generates up to eight single-ended clocks with frequencies from 0.5Hz to 250MHz. LVCMOS output supports 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V. Each output stage can be independently configured.

Clocks generated by the 8A34013 have jitter below 150fs RMS (10kHz to 20MHz) and therefore are suitable for serial 100GBASE-R, 40GBASE-R, and lower rate interfaces.

All control and status registers are accessed through the  $l^2C$  / SPI slave microprocessor interface, the SPI interface mode supports high clock rates (up to 50MHz). For configuring the DPLLs, the  $l^2C$  master interface can automatically load a configuration from an external EEPROM after reset. The 8A34013 also has an internal customer definable One-Time Programmable memory with up to 16 different configurations.

# Contents

| Overview                                          |    |

|---------------------------------------------------|----|

| Typical Applications                              | 1  |

| Features                                          | 1  |

| Block Diagram                                     | 2  |

| Description                                       | 2  |

| Pin Assignments                                   | 10 |

| Pin Descriptions and Pin Characteristics          | 10 |

| Overview of the 8A3xxxx Family                    | 14 |

| Functional Description                            | 14 |

| Basic Functional Blocks                           | 15 |

| Crystal Input (OSCI / OSCO)                       | 15 |

| Frequency Representation                          | 15 |

| System APLL                                       | 15 |

| Input Stage                                       | 16 |

| Reference Monitoring                              | 19 |

| Loss of Signal (LOS) Monitoring                   | 19 |

| Activity                                          |    |

| Timer                                             | 20 |

| Frequency Offset Monitoring                       |    |

| Advanced Input Clock Qualification                |    |

| Input Clock Qualification                         |    |

| Clock Reference Disqualifier through GPIO         |    |

| Frame Pulse Operation                             |    |

| Sync Pulse Operation                              |    |

| Crystal Oscillator Input (XO_DPLL)                |    |

| Digital Phase Locked Loop (DPLL)                  |    |

| Free-Run Mode                                     |    |

| Locked Mode                                       |    |

| Holdover Mode                                     |    |

| Manual Holdover Mode                              |    |

| External Feedback                                 |    |

| DPLL Input Clock Qualification and Selection      |    |

| Automatic Input Clock Selection                   |    |

| Manual Input Clock Selection via Register or GPIO |    |

| Slave or GPIO Slave Selection                     |    |

| DPLL Switchover Management.                       |    |

| Revertive and Non-Revertive Switching             |    |

| Hitless Reference Switching                       |    |

| Phase Slope Limiting.                             |    |

| DPLL Frequency Offset Limit Setting               |    |

| DPLL Fast Lock Operation                          |    |

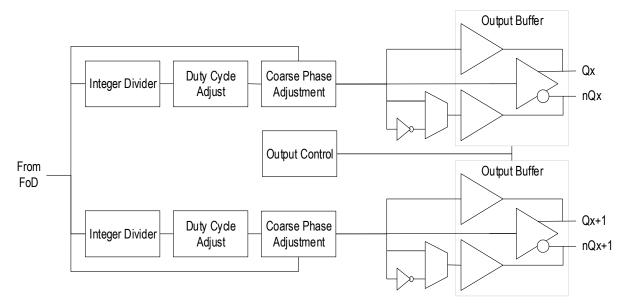

| Steerable Fractional Output Divider (FOD)         |    |

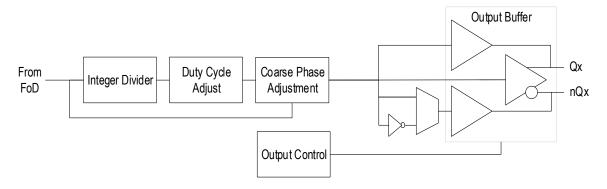

| FOD Multiplexing and Output Stages                |    |

| Integer Output Divider                            |    |

| Output Duty Cycle Adjustment                      |    |

| Output Coarse Phase Adjustment                    |    |

|                                                   |    |

| General Purpose Input/Outputs (GPIOs)             | 35 |

| GPIO Modes                                                                |  |

|---------------------------------------------------------------------------|--|

| GPIO Pin Configuration                                                    |  |

| Alarm Output Operation                                                    |  |

| Device Initial Configuration                                              |  |

| Use of GPIO Pins at Reset                                                 |  |

| Default Values for Registers                                              |  |

| One-Time Programmable (OTP) Memory                                        |  |

| Configuration Data in OTP                                                 |  |

| Use of External I <sup>2</sup> C EEPROM                                   |  |

| Device Updates in External I <sup>2</sup> C EEPROM                        |  |

| Configuration Data in External I2C EEPROM                                 |  |

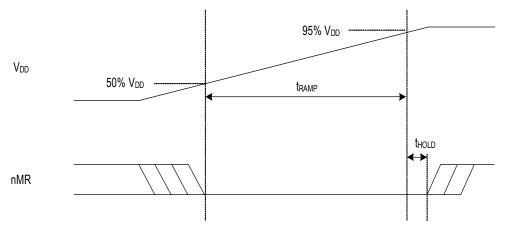

| Reset Sequence                                                            |  |

| Step 0 – Reset Sequence Starting Condition                                |  |

| Step 1 – Negation of nMR (Rising Edge)                                    |  |

| Step 2 – Internally Set Default Conditions                                |  |

| Step 3 – Scan for Device Updates in EEPROM                                |  |

| Step 4 – Read Configuration from OTP                                      |  |

| Step 5 – Search for Configuration in External EEPROM                      |  |

| Step 6 - Load OTP Hotfix and Execute                                      |  |

| Step 7 – Complete Configuration                                           |  |

| Accessing the Serial Ports After a Reset Sequence                         |  |

| Clock Gating and Logic Power-Down Control                                 |  |

| Serial Port Functions                                                     |  |

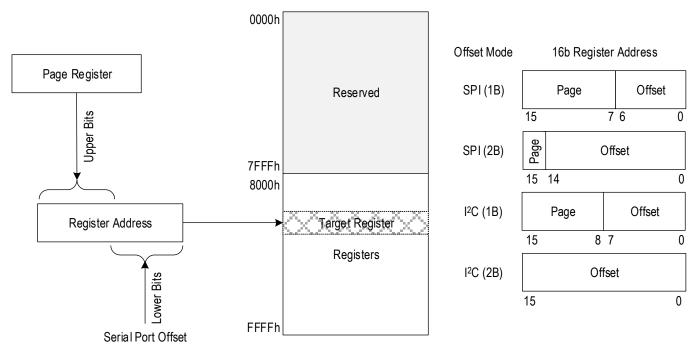

| Addressing Registers within the 8A34013                                   |  |

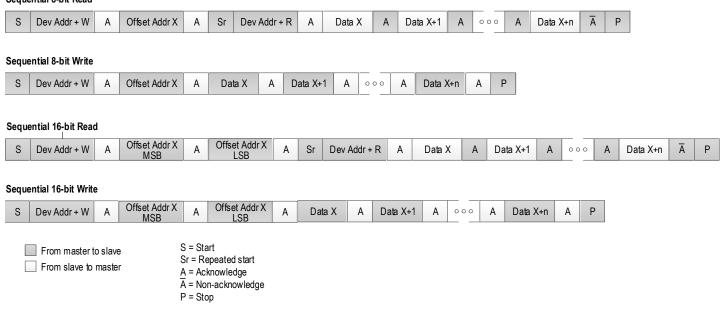

| I2C Slave Operation                                                       |  |

| I2C Master                                                                |  |

| SPI Operation                                                             |  |

| JTAG Interface                                                            |  |

| Basic Operating Modes (Synthesizer / Clock Generator / Jitter Attenuator) |  |

| Free-Running Synthesizer Operation                                        |  |

| Clock Generator Operation                                                 |  |

| Synthesizer Disciplined with Oscillator Operation                         |  |

| Jitter Attenuator Operation                                               |  |

| Jitter Attenuator Operation with External Digital Loop Filter             |  |

| Jitter Attenuator Disciplined with Oscillator Operation                   |  |

| Digitally-Controlled Oscillator Operation via External Control            |  |

| Write-Frequency Mode                                                      |  |

| Increment / Decrement Registers and Pins                                  |  |

| Write-Phase Mode                                                          |  |

| Adjusting Phase while in Closed Loop Operation                            |  |

| Combo Mode                                                                |  |

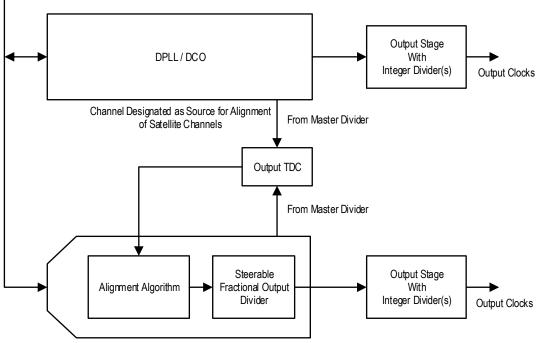

| Satellite Channel                                                         |  |

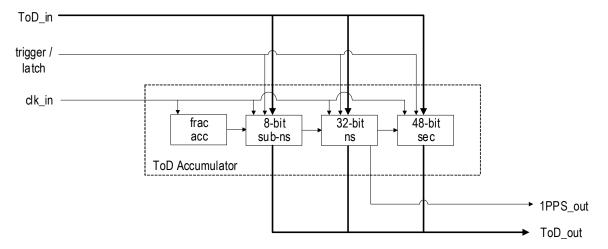

| Time-of-Day (ToD) Operation                                               |  |

| ToD Triggers and Latches                                                  |  |

| GPIO Functions Associated with ToD Operation                              |  |

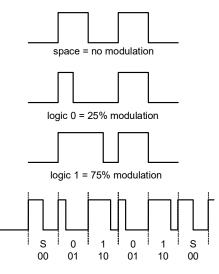

| Pulse-Width Modulation Encoders, Decoders, and FIFO                       |  |

| PWM Signature                                                             |  |

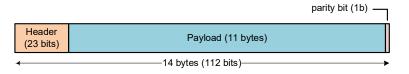

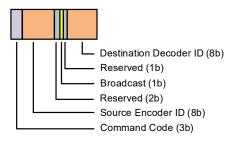

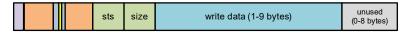

| PWM Frames                                                                |  |

| 1PPS and ToD Distribution (PWM_PPS)                                       |  |

| Multi-Clock Distribution (PWM_SYNC)                         | 65 |

|-------------------------------------------------------------|----|

| Register Read/Write (PWM_READ/PWM_WRITE)                    | 65 |

| External Data Channel (PWM FIFO)                            | 65 |

| Other Operating Modes                                       | 66 |

| AC and DC Specifications                                    | 67 |

| Abbreviations Used in this Section                          | 67 |

| Absolute Maximum Ratings                                    | 68 |

| Recommended Operating Conditions                            | 68 |

| Supply Voltage Characteristics                              | 69 |

| DC Electrical Characteristics                               | 74 |

| AC Electrical Characteristics                               | 82 |

| Clock Phase Noise Characteristics                           |    |

| Applications Information                                    |    |

| Recommendations for Unused Input and Output Pins            | 89 |

| Inputs                                                      | 89 |

| Outputs                                                     | 89 |

| Power Connections                                           |    |

| Clock Input Interface                                       |    |

| Overdriving the XTAL Interface                              |    |

| Wiring the Differential Input to Accept Single-Ended Levels |    |

| Differential Output Termination                             |    |

| Crystal Recommendation                                      |    |

| External I2C Serial EEPROM Recommendation                   |    |

| Schematic and Layout Information                            |    |

| Power Considerations                                        |    |

| VFQFPN EPAD Thermal Release Path                            |    |

| Thermal Characteristics                                     |    |

| Package Outline Drawings                                    |    |

| Marking Diagram                                             |    |

| Ordering Information                                        |    |

| Product Identification                                      |    |

| Glossary                                                    |    |

| Revision History                                            | 97 |

# **List of Figures**

| Figure 1.  | Block Diagram                                                   |    |

|------------|-----------------------------------------------------------------|----|

| Figure 2.  | Pin Assignments for 7 × 7 mm 48-VFQFPN Package – Bottom View    | 10 |

| Figure 3.  | Single PLL Channel                                              | 14 |

| Figure 4.  | System Analog PLL Channel                                       |    |

| Figure 5.  | Input Stage Configured as Differential Only                     | 17 |

| Figure 6.  | Input Stage Configured as Dual Single-Ended                     |    |

| Figure 7.  | Input Stage Configured as Differential Plus Single Single-Ended | 18 |

| Figure 8.  | Frame Pulse Operation                                           | 23 |

| Figure 9.  | Sync Pulse Operation                                            | 23 |

| Figure 10. | DPLL Channel                                                    | 24 |

| Figure 11. | DPLL Automatic State Machine                                    | 25 |

| Figure 12. | External Feedback                                               | 27 |

| Figure 13. | Steerable Fractional Output Divider Block                       | 30 |

| Figure 14. | Single Output Stage                                             | 32 |

| Figure 15. | Dual Output Stage                                               | 32 |

| Figure 16. | Power-Up Reset Sequencing                                       | 41 |

| Figure 17. | Register Addressing Modes via Serial Port                       | 45 |

| Figure 18. | I2C Slave Sequencing                                            | 45 |

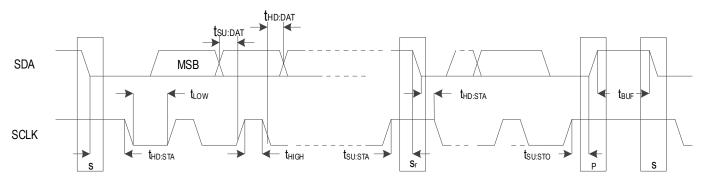

| Figure 19. | I2C Slave Timing Diagram                                        | 47 |

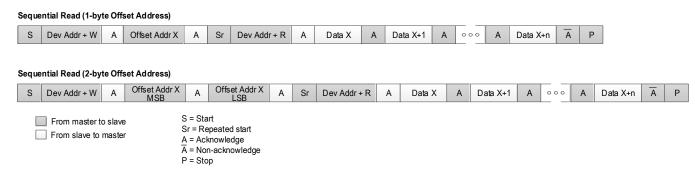

| Figure 20. | I2C Master Sequencing                                           | 47 |

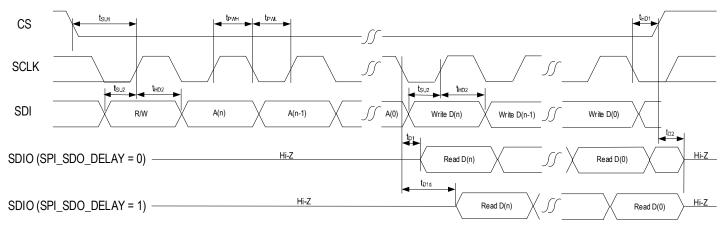

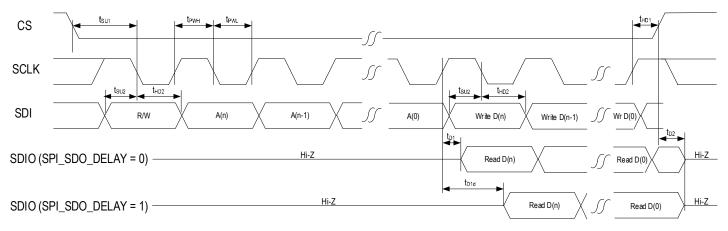

| Figure 21. | SPI Sequencing                                                  | 48 |

| Figure 22. | SPI Timing Diagrams                                             | 50 |

| Figure 23. | Free-Running Synthesizer Operation                              | 52 |

| Figure 24. | Clock Generator Operation                                       | 52 |

| Figure 25. | Synthesizer Disciplined with Oscillator Operation               | 53 |

| Figure 26. | Jitter Attenuator Operation                                     | 53 |

|            | Jitter Attenuator Operation with External Digital Loop Filter   |    |

|            | Jitter Attenuator Disciplined with Oscillator Operation         |    |

| Figure 29. | External DCO Control via Frequency Control Word                 | 55 |

| Figure 30. | External DCO Control via Phase Control Word                     | 56 |

| Figure 31. | Phase Control in Closed Loop Operation                          | 57 |

| Figure 32. | Combo Mode                                                      | 58 |

| Figure 33. | Satellite Channel and Source Channel                            | 59 |

| Figure 34. | ToD Accumulator                                                 | 60 |

| Figure 35. | PWM Coded Symbols                                               | 62 |

| Figure 36. | PWM Signature – 1PPS Encoding Example                           | 63 |

| •          | PWM Frame                                                       |    |

| Figure 38. | PWM Frame Header                                                | 64 |

| Figure 39. | PWM Frame – PWM_PPS                                             | 64 |

|            | PWM Frame – PWM_READ                                            |    |

| Figure 41. | PWM Frame – PWM_WRITE                                           | 65 |

| Figure 42. | User PWM Frame – PWM_USER                                       | 66 |

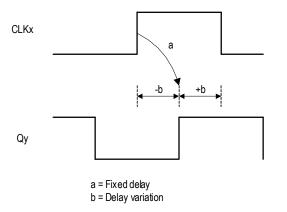

| Figure 43. | Input-Output Delay with Internal Feedback                       | 86 |

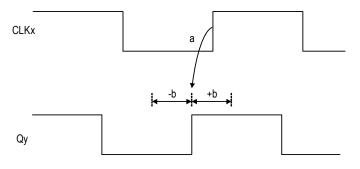

| •          | Input-Output Delay with External Feedback                       |    |

| Figure 45. | 156.25MHz Output Phase Noise                                    | 88 |

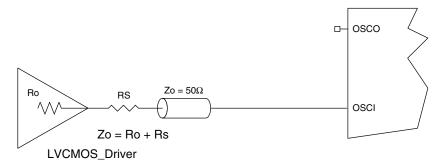

| Figure 46. | 1.8V LVCMOS Driver to XTAL Input Interface                      | 90 |

| -          | LVCMOS Driver to XTAL Input Interface                           |    |

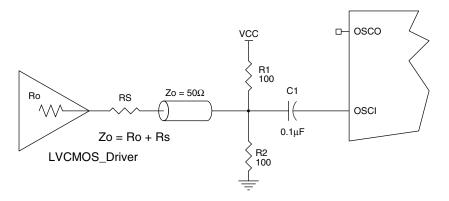

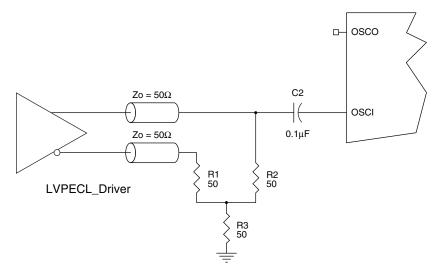

| Figure 48. | LVPECL Driver to XTAL Input Interface                           | 91 |

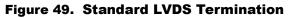

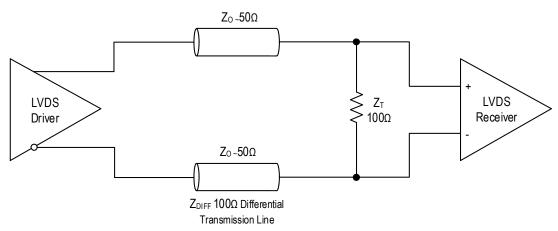

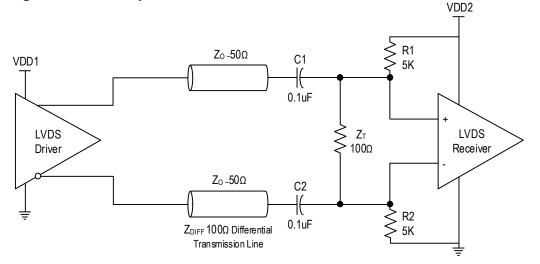

| Figure 49. | Standard LVDS Termination                                                             | <i>)</i> 1 |

|------------|---------------------------------------------------------------------------------------|------------|

| Figure 50. | AC Coupled LVDS Termination                                                           | )2         |

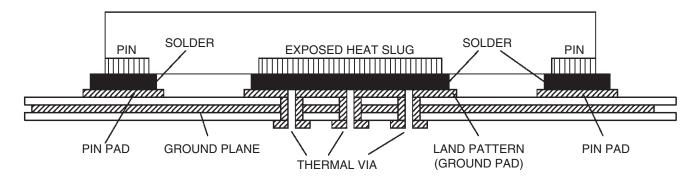

| Figure 51. | P.C. Assembly for Exposed Pad Thermal Release Path – Side View (Drawing not to Scale) | )3         |

# **List of Tables**

| Table 1.  | Pin Descriptions                                                                                                             | 10 |

|-----------|------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.  | Pin Characteristics                                                                                                          | 13 |

| Table 3.  | Related Documentation                                                                                                        | 14 |

| Table 4.  | Input Stage Setting                                                                                                          |    |

| Table 5.  | Input Stages Using GPIOs as Reference Clock Inputs                                                                           | 18 |

| Table 6.  | Gapped Clock LOS Settings                                                                                                    | 19 |

| Table 7.  | Activity Limit                                                                                                               | 20 |

| Table 8.  | Disqualification Timer                                                                                                       | 20 |

| Table 9.  | Qualification Timer                                                                                                          | 21 |

| Table 10. | Frequency Offset Limits                                                                                                      | 21 |

| Table 11. | DPLL Bandwidth                                                                                                               | 26 |

| Table 12. | DPLL Reference Mode                                                                                                          | 27 |

| Table 13. | Some Key DPLL Phase-Slope Limits Supported                                                                                   | 29 |

| Table 14. | FOD to Output Stage to Output Pin Mappings                                                                                   | 31 |

| Table 15. | Output Duty Cycle Examples                                                                                                   | 33 |

| Table 16. | Configurable Output Mode Options                                                                                             | 34 |

| Table 17. | Alarm Indications                                                                                                            | 37 |

| Table 18. | GPIO Pin Usage at Start-Up                                                                                                   | 38 |

| Table 19. | Serial Port Pin to Function Mapping                                                                                          | 44 |

| Table 20. | I2C Slave Timing                                                                                                             | 47 |

| Table 21. | SPI Timing                                                                                                                   | 50 |

| Table 22. | JTAG Signal Mapping                                                                                                          | 51 |

| Table 23. | Abbreviated Signal Names and the Detailed Signal Names Referenced by Them                                                    | 67 |

| Table 24. | Absolute Maximum Ratings                                                                                                     | 68 |

| Table 25. | Recommended Operating Conditions                                                                                             | 68 |

| Table 26. | Power Supply DC Characteristics                                                                                              | 69 |

| Table 27. | Output Supply Current (Output Configured as Differential)                                                                    | 72 |

| Table 28. | Output Supply Current (Output Configured as LVCMOS)                                                                          | 73 |

| Table 29. | LVCMOS/LVTTL DC Characteristics                                                                                              | 74 |

| Table 30. | Differential Input DC Characteristics                                                                                        | 76 |

| Table 31. | Differential Output DC Characteristics (V <sub>DDO Qx</sub> = 3.3V+5%, V <sub>SS</sub> = 0V, T <sub>A</sub> = -40°C to 85°C) | 77 |

| Table 32. | Differential Output DC Characteristics (V <sub>DDO Qx</sub> = 2.5V+5%, V <sub>SS</sub> = 0V, T <sub>A</sub> = -40°C to 85°C) |    |

| Table 33. | Differential Output DC Characteristics (V <sub>DDO Qx</sub> = 1.8V+5%, V <sub>SS</sub> = 0V, T <sub>A</sub> = -40°C to 85°C) |    |

| Table 34. | LVCMOS Clock Output DC Characteristics                                                                                       |    |

| Table 36. | Crystal Characteristics                                                                                                      | 81 |

| Table 35. | Input Frequency Characteristics                                                                                              | 81 |

| Table 37. | AC Characteristics                                                                                                           | 82 |

| Table 38. | Jitter Characteristics                                                                                                       | 87 |

| Table 39. | Recommended Tuning Capacitors for Crystal Input                                                                              |    |

| Table 40. | Thermal Characteristics for 72-pin QFN Package                                                                               |    |

| Table 41. | Pin 1 Orientation in Tape and Reel Packaging.                                                                                |    |

| Table 42: | Product Identification                                                                                                       | 95 |

## **Pin Assignments**

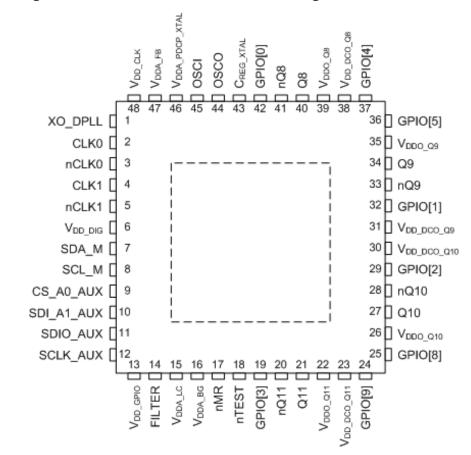

Figure 2. Pin Assignments for 7 × 7 mm 48-VFQFPN Package – Bottom View<sup>[2]</sup>

# **Pin Descriptions and Pin Characteristics**

| Table | 1. | Pin | Descriptions <sup>[a]</sup> |

|-------|----|-----|-----------------------------|

|-------|----|-----|-----------------------------|

| Number | Name                | Туре  |           | Description                                                                                                                  |  |

|--------|---------------------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | XO_DPLL             | Input |           | Single-ended crystal oscillator input for System Digital PLL (for more information, see Crystal Oscillator Input (XO_DPLL)). |  |

| 2      | CLK0                | Input | Pull-down | Positive input for differential input Clock 0 or single-ended input for Clock 0 (for more information, see Input Stage).     |  |

| 3      | nCLK0               | Input | Pull-up   | Negative input for differential input Clock 0 or single-ended input for Clock 8 (for more information, see Input Stage).     |  |

| 4      | CLK1                | Input | Pull-down | Positive input for differential input Clock 1 or single-ended input for Clock 1 (for more information, see Input Stage).     |  |

| 5      | nCLK1               | Input | Pull-up   | Negative input for differential input Clock 1 or single-ended input for Clock 9 (for more information, see Input Stage).     |  |

| 6      | V <sub>DD_DIG</sub> | Power |           | Power supply for digital logic. 1.2V or 1.8V supported.                                                                      |  |

<sup>[2]</sup> Indexed signals (e.g., GPIO[5]) are not necessarily numbered sequentially. Some indexes may be skipped. This is to maintain software compatibility with other members of the family of devices.

# Table 1. Pin Descriptions<sup>[a]</sup>

| Number | Name                    | Ту     | уре                    | Description                                                                                                                                                                                                                                                      |  |  |  |

|--------|-------------------------|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7      | SDA_M                   | I/O    | Pull-up                | I <sup>2</sup> C Bi-directional Data for I <sup>2</sup> C Master Operation (for more information, see I2C Master). It can be connected to SDIO_AUX if desired and the connected port is configured for I <sup>2</sup> C operation. External pull-up recommended. |  |  |  |

| 8      | SCL_M                   | I/O    | Pull-up                | I <sup>2</sup> C Clock Output for I <sup>2</sup> C Master Operation (for more information, see I2C Master). It can be connected to SCLK_AUX if desired and the connected port is configured for I <sup>2</sup> C operation. External pull-up recommended.        |  |  |  |

| 9      | CS_A0_AUX               | Input  | Pull-up                | Auxiliary serial port input. Used as a chip-select input in SPI mode and optionally as an Address Bit 0 select input in I <sup>2</sup> C mode.                                                                                                                   |  |  |  |

| 10     | SDI_A1_AUX              | Input  | Pull-up                | Auxiliary serial port input. Used as Serial Data In in 4-wire SPI mode and optionally as an Address Bit 1 select input in I <sup>2</sup> C mode. Unused in 3-wire SPI mode.                                                                                      |  |  |  |

| 11     | SDIO_AUX                | I/O    | Pull-up                | Auxiliary serial port bi-directional data pin. Used as a bi-directional data pin in $I^2C$ and 3-wire SPI modes. Used as Serial Data Output pin in 4-wire SPI mode. External pull-up recommended in $I^2C$ mode.                                                 |  |  |  |

| 12     | SCLK_AUX                | Input  | Pull-up                | Auxiliary serial port clock input. Used in both SPI and I $^2$ C modes as the clock. External pull-up recommended in I $^2$ C mode.                                                                                                                              |  |  |  |

| 13     | V <sub>DD_GPIO</sub>    | Power  |                        | Power supply for all the digital pins, including GPIO pins and serial ports pins. 3.3V, 2.5V, 1.8V, or 1.5V supported.                                                                                                                                           |  |  |  |

| 14     | FILTER                  | Analog |                        | Reference capacitor for System Analog PLL Loop Filter. Requires a 2.2nF capacitor to ground.                                                                                                                                                                     |  |  |  |

| 15     | V <sub>DDA_LC</sub>     | Power  |                        | Analog power supply voltage for System Analog PLL's LC Resonator, 3.3V or 2.5V supported. $^{\rm [C]}$                                                                                                                                                           |  |  |  |

| 16     | V <sub>DDA_BG</sub>     | Power  |                        | Analog power supply voltage for System Analog PLL's bandgap regulator, 3.3V or 2.5V supported. <sup>[C]</sup>                                                                                                                                                    |  |  |  |

| 17     | nMR                     | Input  | Pull-up                | Master Reset input (for more information, see Device Initial Configuration).                                                                                                                                                                                     |  |  |  |

| 18     | nTEST                   | Input  | Pull-up                | Test Mode enable pin. Must be high for normal operation.                                                                                                                                                                                                         |  |  |  |

| 19     | GPIO[3]                 | I/O    | Pull-up <sup>[b]</sup> | General Purpose Input / Output 3 (for more information, see General Purpose Input/Outputs (GPIOs)).                                                                                                                                                              |  |  |  |

| 20     | nQ11                    | Output |                        | Q11 clock negative output (for more information, see FOD Multiplexing and Output Stages).                                                                                                                                                                        |  |  |  |

| 21     | Q11                     | Output |                        | Q11 clock positive output (for more information, see FOD Multiplexing and Output Stages).                                                                                                                                                                        |  |  |  |

| 22     | V <sub>DDO_Q11</sub>    | Power  |                        | Power supply for Q11/nQ11 output buffers (for more information on supported voltages, see FOD Multiplexing and Output Stages).                                                                                                                                   |  |  |  |

| 23     | V <sub>DD_DCO_Q11</sub> | Power  |                        | Power supply for FOD block supporting output clocks Q11/nQ11. Also powers the FOD control logic for FOD blocks supporting Q10/nQ10 and Q11/nQ11. 1.8V supply required.                                                                                           |  |  |  |

| 24     | GPIO[9]                 | I/O    | Pull-up <sup>[b]</sup> | General Purpose Input / Output 9 (for more information, see General Purpose Input/Outputs (GPIOs)).                                                                                                                                                              |  |  |  |

| 25     | GPIO[8]                 | I/O    | Pull-up <sup>[b]</sup> | General Purpose Input / Output 8 (for more information, see General Purpose Input/Outputs (GPIOs)).                                                                                                                                                              |  |  |  |

| 26     | V <sub>DDO_Q10</sub>    | Power  |                        | Power supply for Q10/nQ10 output buffers (for more information on supported voltages, see FOD Multiplexing and Output Stages).                                                                                                                                   |  |  |  |

### Table 1. Pin Descriptions<sup>[a]</sup>

| Number | Name                       | Ту     | /ре                    | Description                                                                                                                                                                                            |

|--------|----------------------------|--------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27     | Q10                        | Output |                        | Q10 clock positive output (for more information, see FOD Multiplexing and Output Stages).                                                                                                              |

| 28     | nQ10                       | Output |                        | Q10 clock negative output (for more information, see FOD Multiplexing and Output Stages).                                                                                                              |

| 29     | GPIO[2]                    | I/O    | Pull-up <sup>[b]</sup> | General Purpose Input / Output 2 (for more information, see General Purpose Input/Outputs (GPIOs).                                                                                                     |

| 30     | V <sub>DD_DCO_Q10</sub>    | Power  |                        | Power supply for FOD block supporting output clocks Q10/nQ10. 1.8V supply required.                                                                                                                    |

| 31     | V <sub>DD_DCO_Q9</sub>     | Power  |                        | Power supply for FOD block supporting output clocks Q9/nQ9. 1.8V supply required.                                                                                                                      |

| 32     | GPIO[1]                    | I/O    | Pull-up <sup>[b]</sup> | General Purpose Input / Output 1 (for more information, see General Purpose Input/Outputs (GPIOs)).                                                                                                    |

| 33     | nQ9                        | Output |                        | Q9 clock negative output (for more information, see FOD Multiplexing and Output Stages).                                                                                                               |

| 34     | Q9                         | Output |                        | Q9 clock positive output (for more information, see FOD Multiplexing and Output Stages).                                                                                                               |

| 35     | V <sub>DDO_Q9</sub>        | Power  |                        | Power supply for Q9/nQ9 output buffers (for more information on supported voltages, see FOD Multiplexing and Output Stages).                                                                           |

| 36     | GPIO[5]                    | I/O    | Pull-up <sup>[b]</sup> | General Purpose Input / Output 5 (for more information, see General Purpose Input/Outputs (GPIOs)).                                                                                                    |

| 37     | GPIO[4]                    | I/O    | Pull-up <sup>[b]</sup> | General Purpose Input / Output 4 (for more information, see General Purpose Input/Outputs (GPIOs)).                                                                                                    |

| 38     | V <sub>DD_DCO_Q8</sub>     | Power  |                        | Power supply for FOD block supporting output clocks Q8/nQ8. Also powers the FOD control logic for FOD blocks supporting Q8/nQ8 and Q9/nQ9. 1.8V supply required.                                       |

| 39     | V <sub>DDO_Q8</sub>        | Power  |                        | Power supply for Q8/nQ8 output buffers (for more information on supported voltages, see FOD Multiplexing and Output Stages).                                                                           |

| 40     | Q8                         | Output |                        | Q8 clock positive output (for more information, see FOD Multiplexing and Output Stages).                                                                                                               |

| 41     | nQ8                        | Output |                        | Q8 clock negative output (for more information, see FOD Multiplexing and Output Stages).                                                                                                               |

| 42     | GPIO[0]                    | I/O    | Pull-up <sup>[b]</sup> | General Purpose Input / Output 0 (for more information, see General Purpose Input/Outputs (GPIOs)).                                                                                                    |

| 43     | C <sub>REG_XTAL</sub>      | Power  |                        | Filter capacitor for voltage regulator for oscillator circuit associated with OSCI/OSCO pins. Requires a $10\mu$ F filter capacitor to ground.                                                         |

| 44     | OSCO                       | Output |                        | Crystal Output. This pin should be connected to a crystal. If an oscillator is connected to the OSCI pin, this pin should be left unconnected.                                                         |

| 45     | OSCI                       | Input  |                        | Crystal Input. Accepts a reference from a clock oscillator or a fundamental mode parallel-resonant crystal (for information, see Table 35 and Table 36).                                               |

| 46     | V <sub>DDA_PDCP_XTAL</sub> | Power  |                        | Analog power supply voltage for System Analog PLL's phase detector and charge pump, as well as the oscillator circuit associated with OSCI/OSCO pins. 2.5V or 3.3V operation supported. <sup>[C]</sup> |

### Table 1. Pin Descriptions<sup>[a]</sup>

| Number | Name                | Name Type Description |                                                                                                                                                                   |

|--------|---------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47     | V <sub>DDA_FB</sub> | Power                 | Analog power supply voltage for System Analog PLL's feedback divider; 1.8V required.                                                                              |

| 48     | V <sub>DD_CLK</sub> | Power                 | Power supply for input clock buffers and dividers. Supports 1.8V, 2.5V, or 3.3V as appropriate for the input clock swing (for more information, see Input Stage). |

| ePAD   | V <sub>SS</sub>     | Power                 | Device ePAD must be connected to Ground.                                                                                                                          |

[a] Pull-up and Pull-down refer to internal input resistors (for typical values, see Table 2.

[b] GPIO pins can be configured via EEPROM and/or OTP with a pull-up or pull-down. Pull-up is the default configuration.

[c] V<sub>DDA\_PDCP\_XTAL</sub>, V<sub>DDA\_LC</sub>, and V<sub>DDA\_BG</sub> can be driven with either 2.5V or 3.3V, however all must use the same voltage level. Register programming is required to configure the device for either 2.5V or 3.3V operation. For information, see the 8A3xxxx Family Programming Guide.

#### **Table 2. Pin Characteristics**

| Symbol                          | Parar                                                 | neter                     | Test Conditions                             | Minimum              | Typical | Maximum | Units |

|---------------------------------|-------------------------------------------------------|---------------------------|---------------------------------------------|----------------------|---------|---------|-------|

|                                 |                                                       | OSCI, OSCO                |                                             |                      | 9       |         |       |

| C <sub>IN</sub>                 | Input Capacitance                                     | XO_DPLL                   |                                             |                      | 1       |         | pF    |

|                                 |                                                       | All Other pins            |                                             |                      | 2       |         |       |

| R <sub>PULLUP</sub>             | Input Pullup<br>Resistor                              | nCLK[1:0]                 |                                             |                      | 50      |         | kΩ    |

| R <sub>PULLDOWN</sub>           | Input Pulldown<br>Resistor                            | CLK[1:0]                  |                                             |                      | 50      |         | kΩ    |

|                                 |                                                       |                           | V <sub>DDO_Qx</sub> <sup>[a]</sup> = 3.465V |                      | 9       |         |       |

|                                 |                                                       |                           | V <sub>DDO_Qx</sub> = 2.625V                |                      | 8.8     |         |       |

|                                 | Power Dissipation<br>Capacitance<br>(per output pair) | LVCMOS                    | $V_{DDO_Qx} = 1.89V$                        |                      | 8.8     |         | pF    |

| C <sub>PD</sub>                 |                                                       |                           | V <sub>DDO_Qx</sub> = 1.575V                |                      | 9.2     |         |       |

| ObD                             |                                                       |                           | $V_{DDO_Qx} = 1.26V$                        |                      | 8.7     |         |       |

|                                 |                                                       |                           | $V_{DDO_Qx} = 3.465V$                       |                      | 1.4     |         |       |

|                                 |                                                       | Differential              | $V_{DDO_Qx} = 2.625V$                       |                      | 3.5     |         |       |

|                                 |                                                       |                           | $V_{DDO_Qx} = 1.89V$                        |                      | 5       |         |       |

|                                 |                                                       |                           | $V_{DD_GPIO} = 3.3V$                        |                      | 30      |         |       |

|                                 |                                                       | GPIO[9:8,5:0]             | $V_{DD_GPIO} = 2.5V$                        |                      | 31      |         | - Ω   |

|                                 |                                                       | 0110[0.0,0.0]             | $V_{DD_GPIO} = 1.8V$                        |                      | 32      |         |       |

| R <sub>OUT</sub> <sup>[b]</sup> | Output                                                |                           | $V_{DD_{GPIO}} = 1.5V$                      |                      | 33      |         |       |

|                                 | Impedance                                             |                           | $V_{DD_GPIO} = 3.3V$                        |                      | 27      |         |       |

|                                 |                                                       | SCL_M, SDA_M,<br>SDIO_AUX | $V_{DD_GPIO} = 2.5V$                        |                      | 30      |         |       |

|                                 |                                                       |                           | $V_{DD_GPIO} = 1.8V$                        |                      | 38      |         |       |

|                                 |                                                       |                           |                                             | $V_{DD_GPIO} = 1.5V$ |         | 47      |       |

[a]  $V_{DDO_{Qx}}$  denotes:  $V_{DDO_{Q8}}$ ,  $V_{DDO_{Q9}}$ ,  $V_{DDO_{Q10}}$ , or  $V_{DDO_{Q11}}$

[b] Output impedance values for the Qx / nQx outputs are provided in Table 34.

# **Overview of the 8A3xxxx Family**

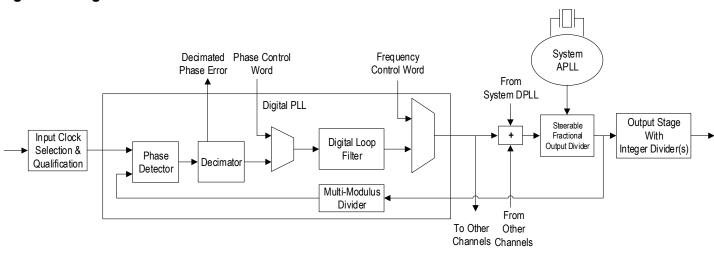

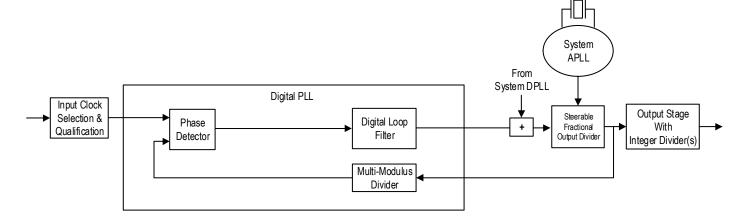

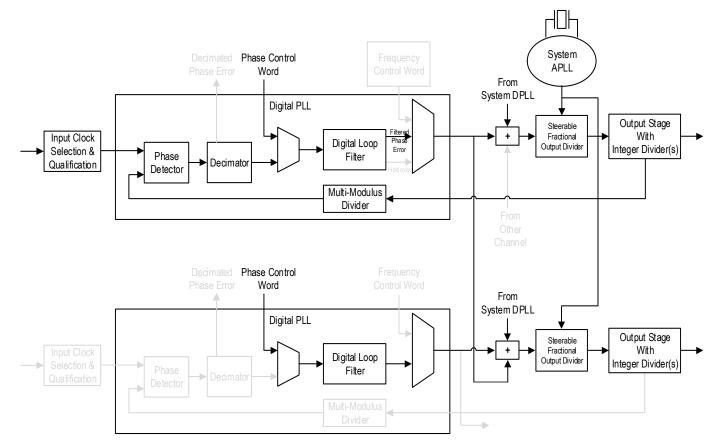

The 8A3xxxx family of devices have multiple channels that can operate independently from each other, or in combination with each other (Combo Mode). All devices share a common channel architecture (see Figure 3) with different functional blocks within the channel being available for use in different members of the family. In addition, there are other peripheral blocks that may only be available in specific family members. The number of channels and of certain peripheral blocks (such as extra serial ports) will also vary from one device in the family to another. Across all members of the family, numbering of the functional and peripheral blocks and their associated register locations are kept consistent to enhance software compatibility and portability between members of the family.

The remaining sub-sections of this Functional Description section will describe functions within the clocking channel and peripheral functions that are available in the 8A34013.

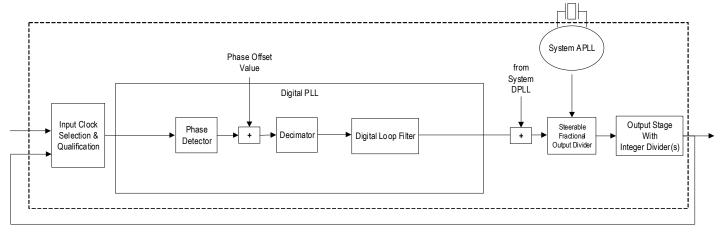

#### Figure 3. Single PLL Channel

# **Functional Description**

This section describes the operational modes and associated functional blocks of the 8A34013. In addition, there are several other areas of the document that describe specific functions or details that would overly burden this document. Table 3 shows related documents.

#### **Table 3. Related Documentation**

| Document Title                                    | Document Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8A34013 Datasheet (This document)                 | Contains a functional overview of the device and hardware-design related details including pinouts, AC and DC specifications, and applications information related to power filtering and terminations.                                                                                                                                                                                                                                                                                                          |

| 8A34013- <dash code=""> Datasheet Addendum</dash> | Indicates pre-programmed power-up / reset configurations of this specific "dash code" part number.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                   | Contains detailed register descriptions and address maps for all members of the family of devices. Please ensure to use the version indicated here for this product.                                                                                                                                                                                                                                                                                                                                             |

| 8A3xxxx Family Programming Guide (v4.8)           | The functionality described in this datasheet assumes that the device is running<br>the update revision referred to here or a later one. For individual updates to<br>determine differences between update revisions, see Release Note documents.<br>Note that the device may not ship from the factory with the indicated update<br>revision included in the device. If this is the case, the indicated revision may need<br>to be loaded from an external EEPROM or over the serial port at each device reset. |

# **Basic Functional Blocks**

# Crystal Input (OSCI / OSCO)

The 8A34013 requires a 25MHz–54MHz crystal input on the OSCI/OSCO pins at all times. This input is used to drive the System APLL, which in turn is the source for all internal clocks. For more information, see Table 35 and Crystal Recommendation.

Alternatively, the crystal input can be overdriven by a crystal oscillator. For more information, see Overdriving the XTAL Interface.

### **Frequency Representation**

The format for representing a frequency in the registers of the 8A34013 is:

$f = \frac{M}{N}$  where M is a 48-bit integer and N is a 16-bit integer

The  $\frac{M}{N}$  notation allows non-integer frequencies to be precisely represented as fractions.

For example, the Optical Transport Network OTN OTU2e rate:

$f = 156,250,000 \times \frac{66}{64} \times \frac{255}{237} Hz$

Then:

$$\begin{split} \frac{M}{N} &= 156, 250, 000 \times \frac{66}{64} \times \frac{255}{237} Hz \\ \frac{M}{N} &= (2^4 \times 5^{10}) \times \frac{2^1 \times 3^1 \times 11^1}{2^6} \times \frac{3^1 \times 5^1 \times 17^1}{3^1 \times 79^1} Hz \\ \frac{M}{N} &= \frac{3^1 \times 5^{11} \times 11^1 \times 17^1}{2^1 \times 79^1} Hz \\ \frac{M}{N} &= \frac{27, 392, 578, 125}{158} Hz \\ \end{split}$$

Express terms as the products of prime factors

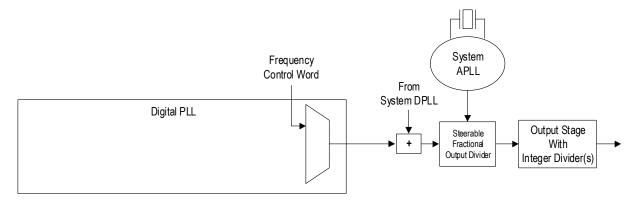

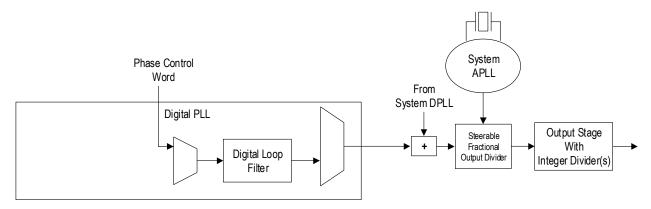

# System APLL

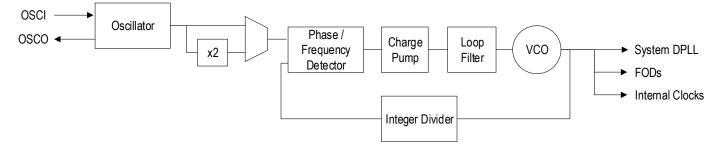

The System APLL is managed with bit fields in the SYS\_APLL module. See Module: SYS\_APLL in the 8A3xxxx Family Programming Guide.

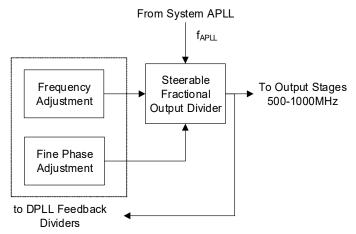

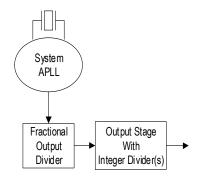

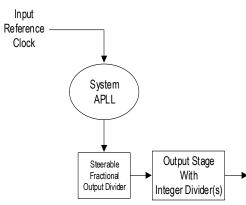

The System APLL is shown in Figure 4. This consists of a simple analog PLL circuit that takes a reference crystal input and multiplies it up to a frequency in the 13.4-13.9GHz range. That high-speed signal is then used to drive the Fractional Output Divider (FOD) circuits as described in FOD Multiplexing and Output Stages. This combination of the System APLL and the FOD logic results in excellent phase noise performance and a substantial amount of flexibility in frequency and phase for the 8A34013. See the SYS\_APLL.SYS\_APLL\_CTRL bit field.

One user programming option involves selecting whether the crystal reference frequency is to be used directly or run through an internal frequency doubler circuit first. An additional user programming option is to select the feedback divider value from the set of integers between 108 and 556. Between these two settings, the user should select a System APLL operating frequency that is within the above-stated tuning range. See the SYS\_APLL\_SYS\_APLL\_CTRL bit field.

### Figure 4. System Analog PLL Channel

During a device reset, the System APLL is configured by loading the appropriate control register fields from the internal One-Time Programmable memory or an external serial EEPROM, whichever is enabled and has valid contents. After the reset sequence has completed, the System APLL can be re-configured manually over the serial port at any time.

The System APLL is considered locked when the Loop Filter control voltage is within specified limits for the configuration selected. The 8A34013 automatically calculates these limits based on other parameters specified in the device configuration. Specific user input to set locking limits is not required. A System APLL Loss-Of-Lock alarm is generated internally. This can be read from internal status registers and/or used to drive a GPIO status signal as described in GPIO Modes. See the STATUS.SYS\_APLL\_STATUS bit field.

### **Input Stage**

The input stage is managed with bit fields in the INPUT\_n modules where n ranges from 0 to 15. See Module: INPUT\_0 in the 8A3xxxx Family Programming Guide.

The 8A34013 contains multiple input stages. An input stage can be configured as one differential or dual single-ended inputs. Some of the input stages can also be configured to support one differential plus one single-ended clock. For information on how to connect various input types to the 8A34013, see Table 4 and Applications Information. See the INPUT\_0.IN\_MODE bit field.

|                |                              | Settings to Use     |                             |      |

|----------------|------------------------------|---------------------|-----------------------------|------|

|                |                              |                     | V <sub>DD_CLK</sub> Voltage |      |

| Input Protocol | Driver V <sub>DD</sub> Level | 3.3V                | 2.5V                        | 1.8V |

| PECL           | 3.3V                         |                     | Differential + NMOS         |      |

| PECL           | 2.5V                         | Differential + PMOS |                             |      |

| LVDS           | N/A                          | Differential + NMOS |                             |      |

| HCSL           | N/A                          | Differential + PMOS |                             |      |

| CML            | 3.3V                         | Differential + NMOS |                             |      |

| CML            | 2.5V                         | Differential + NMOS |                             |      |

| CML            | 1.8V                         | Differential + NMOS |                             |      |

| CMOS           | 3.3V                         |                     |                             |      |

| CMOS           | 2.5V                         | Single-ended        |                             |      |

| CMOS           | 1.8V                         | 1                   |                             |      |

#### Table 4. Input Stage Setting

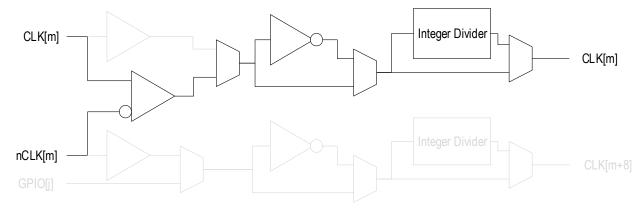

When programmed as differential only, as shown in Figure 5, the internal signal will be referred to by the index number of the input pins (e.g., CLK0 is used to refer to the differential input pair CLK0/nCLK0). It is also necessary to select the appropriate mode, PMOS or NMOS so the input buffer will work best with the incoming signal's voltage swing. See the INPUT\_0.IN\_MODE bit field.

#### Figure 5. Input Stage Configured as Differential Only

The 8A34013 supports input frequencies up to 1GHz for differential inputs. If the input reference clock frequency is higher than 150MHz, then it must be divided down to the internal frequency (less than or equal to 150MHz) used by the DPLL. An integer divider with a range between 2 to 65536 is provided to divide the signal down to less than or equal to 150MHz. For input reference clock frequencies less than 150MHz, the internal divider can be bypassed. See the INPUT\_0.IN\_MODE bit field.

The 8A34013 has the option to lock to the rising or falling edge of the input clock signal by selecting the inverted input path to the divider.

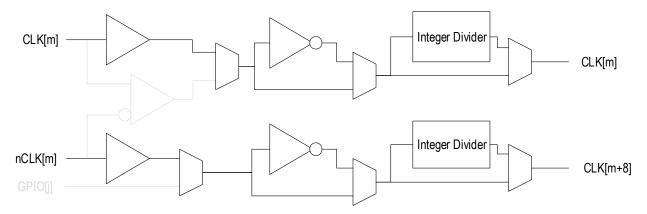

When programmed as dual single-ended as shown in Figure 6, two independent inputs are provided to the 8A34013. The input clock originating from the positive input will be referred to by using the same index number (e.g., CLK0 is used to refer to the signal originating from CLK0). The signal originating from the negative input will be referred to by using the index + 8 (e.g., CLK8 is used to refer to the signal originating from nCLK0). Note that this numbering scheme remains the same on all 8A3xxxx family members, regardless of the number of actual input pins. This is to simplify software portability between family members. PMOS versus NMOS mode does not have any effect for single-ended inputs. See the INPUT\_0.IN\_MODE bit field.

The 8A34013 supports input frequencies up to 250MHz for single-ended inputs. If the input reference clock frequency is higher than 150MHz, then it needs to be divided down to the internal frequency (less or equal to 150MHz) used by the DPLL with the dividers shown in each path. For input reference clock frequencies less than 150MHz, the internal divider can be bypassed. See the INPUT\_0.IN\_MODE bit field.

The 8A34013 has the option to lock to the rising or falling edge of the input clock signal for either path independently. See the INPUT\_0.IN\_MODE bit field.

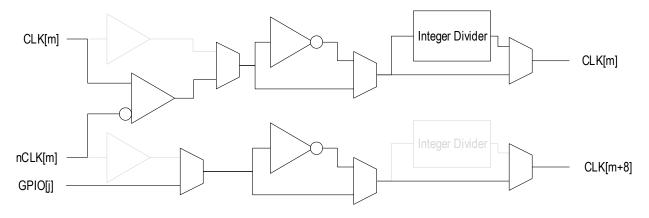

When programmed as differential plus one single-ended as shown in Figure 7, two independent inputs are provided to the 8A34013. This mode can only be used with the GPIOs and input stages shown in the following table. See the INPUT\_0.IN\_MODE bit field.

| Differential Clock Input | Mapped to Internal Clock | GPIO Input | Mapped to Internal Clock |

|--------------------------|--------------------------|------------|--------------------------|

| CLK0 / nCLK0             | CLK[0]                   | GPIO[0]    | CLK[8]                   |

| CLK1 / nCLK1             | CLK[1]                   | -          | CLK[9]                   |

| -                        | -                        | GPIO[3]    | CLK[15]                  |

Input stages not shown in this table can be used in the differential only mode or dual single-ended mode only. The differential input clock originating from the positive input will be referred to the same way as in differential only mode. The signal originating from the GPIO input will be referred to by using the index shown in the table. Note that this numbering scheme remains the same on all 8A3xxxx family members, regardless of the number of actual input pins. This is to simplify software portability between family members. PMOS versus NMOS mode does not have any effect for GPIO inputs. See the INPUT\_0.IN\_MODE bit field.

The 8A34013 supports input frequencies up to 150MHz for GPIO inputs, so no division is necessary. If the input reference clock frequency from the differential input path is higher than 150MHz, then it needs to be divided down to the internal frequency (less or equal to 150MHz) used by the DPLL with the divider shown in its path. For input reference clock frequencies less than 150MHz, the internal divider may be bypassed. See the INPUT\_0.IN\_DIV bit field.

The 8A34013 has the option to lock to the rising or falling edge of the input clock signal for either path individually. See the INPUT\_0.IN\_MODE bit field.

In addition to the above, there are a number of other configuration bits that can be used for the input stage.

- Unused inputs can be disabled. This allows a small amount of power saving and eliminates a source of on-die noise.

- Any input can be used either as a sync or frame pulse associated with an input clock (for more information, see Frame Pulse Operation and Sync Pulse Operation).

- The frequency of each input needs to be known by the 8A34013 and so must be programmed in the registers for each active input stage. See the INPUT\_0.IN\_FREQ bit field.

### **Reference Monitoring**

The reference monitors are managed with bit fields in the REF\_MON\_n and GPIO\_n modules where n ranges from 0 to 15 and the STATUS and ALERT\_CFG modules. See Module: REF\_MON\_0, Module: GPIO\_0, Module: STATUS and Module: ALERT\_CFG in the 8A3xxxx Family Programming Guide.

The quality of all input clocks is always monitored for:

- LOS (loss of signal)

- Activity

- Frequency

All input clocks are monitored all the time, including the active reference to ensure that it is still a valid reference. If any monitor detects a failure of the input clock, it will generate an internal alarm. An input clock with an alarm condition is not used for synchronization unless configured to allow it to be considered qualified in spite of the alarm.

For information on how these internal alarms can be signaled and monitored by outside resources, see Alarm Output Operation.

### Loss of Signal (LOS) Monitoring

Each input clock is monitored for loss of signal (LOS). The LOS reference monitor supports normal clock operation and gapped clock operation. In normal operation, the user can specify whether the alarm condition should be tight to the expected clock period or loose. Tight monitoring will give minimum response time for loss of the input clock, but may result in false alarms due to normal clock jitter or wander. The loose threshold will take longer to detect an alarm condition but is unlikely to give false alarms. For clocks greater than 500kHz, both loose and tight specifications check for the clock edge being outside  $\pm 20$ nsec of the expected position to declare an alarm. For clocks less than or equal to 500kHz, loose threshold is set at  $\pm 25\%$  of the nominal edge position and tight is set to  $\pm 1\%$ . See the REF\_MON\_0.IN\_MON\_LOS\_TOLERANCE, REF\_MON\_0.IN\_MON\_LOS\_CFG bit fields.

In gapped clock operation, LOS is declared if the clock reference misses consecutive clock cycles. It is cleared once an active clock edge is detected. The number of consecutive clocks that are missed to declare LOS is programmable according to Table 6. A setting of 01 is equivalent to a normal clock monitor. See the REF\_MON\_0.IN\_MON\_LOS\_CFG bit field.

| LOS_GAP[2:1] | Number of Consecutive Clocks<br>Missed to Declare LOS |

|--------------|-------------------------------------------------------|

| 00           | Gapped Clock Monitoring<br>Disabled (default)         |

| 01           | 1                                                     |

| 10           | 2                                                     |

| 11           | 5                                                     |

### Table 6. Gapped Clock LOS Settings

There is a status register for LOS. LOS failure alarm will be set as described above. What actions are taken in the event of an alarm can be configured via registers. The LOS failure can cause a specific alarm on a GPIO and/or be used as one input to an Alert (aggregated alarm) output via GPIO if so configured. See the REF\_MON\_0.IN\_MON\_CFG, STATUS.IN0\_MON\_STATUS, ALERT\_CFG.IN1\_0\_MON\_ALERT\_MASK, GPIO\_0.GPIO\_LOS\_INDICATOR, and GPIO\_0.GPIO\_CTRL bit fields.

### Activity

All input reference clocks higher than 1kHz can be monitored for activity. Activity monitoring can quickly determine if a clock is within the frequency limits shown in Table 7. The method used by this monitor is not as precise as the Frequency Offset Monitor, but results are available much more quickly. See the REF\_MON\_0.IN\_MON\_ACT\_CFG bit field.

### Table 7. Activity Limit

| ACT_LIM[2:0] | Range    |

|--------------|----------|

| 000          | ±1000ppm |

| 001          | ±260ppm  |

| 010          | ±130ppm  |

| 011          | ±83ppm   |

| 100          | ±65ppm   |

| 101          | ±52ppm   |

| 110          | ±18ppm   |

| 111          | ±12ppm   |

An activity failure alarm will be set if the input frequency has drifted outside the range set by the programmable range for longer than the period programmed for the activity disqualification timer. What actions are taken in the event of an alarm can be configured via registers. The Activity alarm can be used as one input to an Alert (aggregated alarm) output via GPIO if so configured. See the STATUS.IN0\_MON\_STATUS, REF\_MON\_0.IN\_MON\_CFG, ALERT\_CFG.IN1\_0\_MON\_ALERT\_MASK and GPIO\_0.GPIO\_CTRL bit fields.

### Timer

There is a timer associated with the activity qualification and disqualification of each input reference.

After an activity or LOS alarm is detected, then the timer starts. If the Activity or LOS alarm remains active for the full duration of the timer, then the reference disqualification alarm will be set to high. Register bits can be used to configure whether or not either the alarm is allowed to affect the disqualification decision or not. The disqualification timer can be selected according to Table 8. See the STATUS.IN0\_MON\_STATUS, REF\_MON\_0.IN\_MON\_ACT\_CFG, and ALERT\_CFG.IN1\_0\_MON\_ALERT\_MASK bit fields.

#### **Table 8. Disqualification Timer**

| DSQUAL_TIMER[4:3] | Description    |

|-------------------|----------------|

| 00                | 2.5s (default) |

| 01                | 1.25ms         |

| 10                | 25ms           |

| 11                | 50ms           |

After a reference is disqualified, once it returns (all alarms now clear), then a qualification timer is started. If the alarms remain cleared for the full duration selected, then the input is qualified for use again. Qualification timer settings are shown in Table 9. See the REF\_MON\_0.IN\_MON\_ACT\_CFG bit field.

### Table 9. Qualification Timer

| QUAL_TIMER[6:5] | Description                         |

|-----------------|-------------------------------------|

| 00              | 4 times the Disqualification timer  |

| 01              | 2 times the Disqualification timer  |

| 10              | 8 times the Disqualification timer  |

| 11              | 16 times the Disqualification timer |

### **Frequency Offset Monitoring**

Each input reference is monitored for frequency offset failures. The device measures the input frequency and an alarm is raised if the input frequency exceeds the rejection range limit set as per Table 10. To avoid having the alarm toggling in case an input clock frequency is on the edge of the frequency range, a separate, narrower acceptance range must be met before the alarm will clear. The acceptance ranges are also listed in Table 10. See the REF\_MON\_0.IN\_MON\_CFG, REF\_MON\_0.IN\_MON\_FREQ\_CFG, STATUS.IN0\_MON\_STATUS, ALERT\_CFG.IN1\_0\_MON\_ALERT\_MASK and GPIO\_0.GPIO\_CTRL bit fields.

#### Table 10. Frequency Offset Limits

| FREQ_OFFS_LIM[2:0] | Acceptance Range | Rejection Range | Description                            |

|--------------------|------------------|-----------------|----------------------------------------|

| 000                | ±9.2 ppm         | ±12 ppm         | Stratum 3, Stratum 3E, G.8262 option 2 |

| 001                | ±13.8 ppm        | ±18 ppm         |                                        |

| 010                | ±24.6 ppm        | ±32 ppm         |                                        |

| 011                | ±36.6 ppm        | ±47.5 ppm       |                                        |

| 100                | ±40 ppm          | ±52 ppm         | SONET Minimum clock. G.813 option 2    |

| 101                | ±52 ppm          | ±67.5 ppm       |                                        |

| 110                | ±64 ppm          | ±83 ppm         |                                        |

| 111                | ±100 ppm         | ±130 ppm        |                                        |

### **Advanced Input Clock Qualification**

In addition to the Input Clock Selection and Qualification functions mentioned earlier, the following modes are also available.

### **Input Clock Qualification**

For each DPLL the following conditions must be met for the input clock to be valid; otherwise, it is invalid:

- No reference monitor alarms are asserted for that input clock (unless register settings allow the alarms not to affect the decision)

- GPIO used to disqualify that input reference clock is not asserted

### **Clock Reference Disqualifier through GPIO**