概要

説明

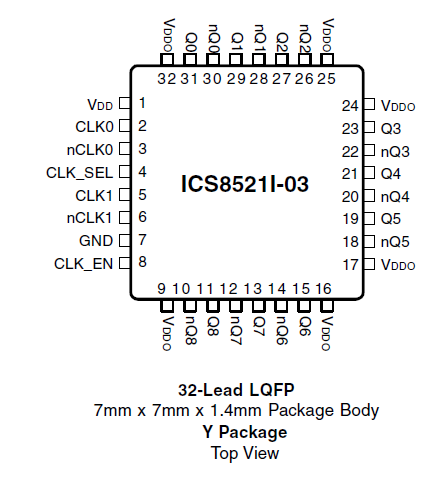

The 8521I-03 is a low skew, 1-to-9 differential-to-LVHSTL fanout buffer. The device has two selectable clock inputs. Redundant clock pairs, CLK0, nCLK0 and CLK1, nCLK1 can accept most standard differential input levels. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/de-assertion of the clock enable pin.

Guaranteed output skew and part-to-part skew characteristics make the 8521I-03 ideal for today’s most advanced applications, such as IA64 and static RAMs.

特長

- 9 LVHSTL outputs

- Redundant differential CLK0, nCLK0 and CLK1, nCLK1 inputs

- CLKx, nCLKx pairs can accept the following differential input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Maximum output frequency: 500MHz

- Output skew: 50ps (maximum)

- Part-to-Part skew: 250ps (maximum)

- Propagation delay: 1.6ns (maximum)

- VOH = 1V (maximum)

- 3.3V core, 1.8V output operating supply voltages

- -40 °C to 85 °C ambient operating temperature

製品比較

アプリケーション

設計・開発

製品選択

適用されたフィルター