概要

説明

The ADC1413D080HN is a dual-channel 14-bit analog-to-digital converter (ADC) optimized for high dynamic performances and low power at sample rates of 80Msps. Pipelined architecture and output error correction ensure the ADC1413D080HN is accurate enough to guarantee zero missing codes over the entire operating range. Supplied from a 3.3V source for analog and a 1.8V source for the output driver, it has two serial outputs, because of the two lanes of differential outputs, which are compliant with the JESD204A standard. An integrated serial peripheral interface (SPI) allows the user to easily configure the ADC. A set of IC configurations is also available via the binary level control pins taken, which are used at power-up.

特長

- 2 configurable serial outputs

- 3.3V, 1.8V single supplies

- Compliant with JESD204A serial transmission standard

- Dual channel 14-bit pipelined ADC core

- Duty cycle stabilizer

- Flexible input voltage range: 1V (p-p) to 2V (p-p) with 6dB programmable fine gain

- High IF capability

- Input bandwidth, 600MHz

- Offset binary, 2s complement, gray code

- Power dissipation, 995mW at 80Msps

- Power-down and Sleep modes

- Sample rate up to 80Msps

- SFDR, 90dBc

- SNR, 73dB

- SPI interface

製品比較

アプリケーション

設計・開発

ボード&キット

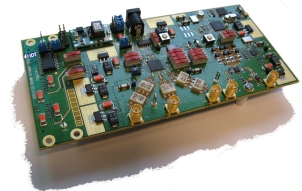

ADC1413D080W1 Demo board With FPGA

IDT's ADC demoboard is suitable for dynamic performance evaluations from low to high IF configuration. The FPGA eases the evaluation and analysis of the ADC dynamic and enables use of the full JESD204A feature set.

ADC1413D080W2 demo board, Lattice ECP3 on board

Our ADC promotional board with on Board Lattice ECP3-70 FPGA enable usage of JESD204A full features sets. This demonstration board enables one channel ADC dynamic performance evaluation for analog input up to 30 MHz

ADC1413D080W0 demoboard; compliant with Lattice, Altera, Xilinx FPGA boards through specific connectors

Our ADC demonstration board is suitable for dynamic performances evaluation from low to high IF configuration. A FPGA mother board (Xilinx, Altera, and Lattice) could be connected to ease the evaluation and analysis of the ADC dynamic and enable usage of the JESD204A full features sets

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター