概要

説明

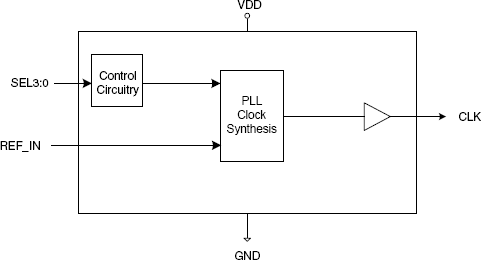

The 662-03 provides synchronous clock generation for audio sampling clock rates derived from an HDTV stream. The device uses the latest PLL technology to provide superior phase noise and long term jitter performance. The device also supports a 27 MHz output clock for video MPEG applications from an HDTV reference clock. Please contact IDT if you have a requirement for an input and output frequency not included here.

特長

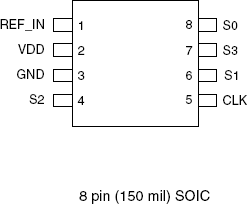

- Packaged in 8-pin SOIC

- Pb (lead) free package, RoHS compliant

- HDTV clock input

- Low phase noise

- Exact (0 ppm) multiplication ratios

- Support for 256 and 384 times sampling rate

- Supports 27 MHz output for video (MPEG)

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター